Kombinációs elemek

Kezdőlap | Rólunk | visszacsatolás

Az adder zsetonok (angol kiegészítők), ahogyan a neve is sugallja, két bemeneti bináris kód összegzésére szolgálnak, vagyis a kimeneti kód megegyezik a két bemeneti kód számtani összegével. Például, ha egy bemeneti kód 7 (0111) és a második 5 (0101), akkor a teljes kód a kimeneten 12 (1100). Az N bitek számával rendelkező két bináris szám összege lehet a számjegyek száma (N + 1). Például, ha a 13 (1101) és a 6 (0110) számokat összegezi, a 19 számot (10011) kapja meg. Ezért az adder kimenetének száma egynél több, mint a bemeneti kódok bitjeinek száma. Ez a kiegészítő (senior) bit az átviteli kimenetnek nevezzük.

Az áramkörökben a nyarakat az SM betűk jelölik. A belföldi sorozatban az adder IC-jét jelző kód IM.

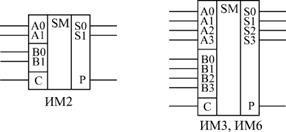

A számlálók egyszámjegyűek (két egyszámjegyű számok összegzéséhez), 2-bites (kétszámjegyű számok feltöltése) és 4-jegyűek (4-jegyű számok hozzáadása). A leggyakoribb használat a 4 bites adder. Az 1. ábrán. A 6.1. Ábrán például a 2-bites és a 4 bites összegzőket mutatjuk be. IM6 chip eltér IM3 csak nagyobb sebesség és számok csapok működni történik ugyanaz.

Ábra. 6.1. Példák a kiegészítő IC-kre

A hordozó összegének és kimenetének kimeneti bitjein kívül az adderek kiterjesztett bemenettel (újabb név az átviteli bemenet) C több adathalmaz kombinálására a bit kapacitás növelése érdekében. Ha ez a bemenet érkezik, a kimenetet egyenként növekszik, és ha nulla, a kimenet nem növekszik. Ha az adder egy IC-jét használja, akkor annak C kiterjesztése nulla legyen.

Például a táblázatban. A 6.1. Ábra bemutatja a 2-bites IM2 adder teljes igazságtábláját. Amint a táblázatból látható, a kimeneti 3-bites kód (P, S1, S0) egyenlő az összege bemenet 2-bites kód (A1, A0) és (B1, B0), és a jel S. Zero szinten - az alsó első szintű - vezető . A 4 bites adder teljes igazatáblája túl nagy lesz, ezért nem adható meg. De a munka lényege pontosan ugyanaz, mint a 2 bites adder esetében.

A számlálók a negatív logikában levő számok összegzésére is használhatók (ha a logikai egység egy elektromos nulla értéket és fordítva, egy elektromos egység logikai zérusnak felel meg). De ebben az esetben a C átvitel bemeneti jele inverz lesz is, tehát amikor egy C-bemenetet használ, akkor egy villamos egységet (nagy feszültségszint) kell alkalmazni. A P átvitel kimeneti jele inverz, az alacsony feszültségszint (elektromos nulla) az átvitel jelenlétének felel meg. Vagyis kiderül, hogy az adder ugyanúgy működik mind pozitív, mind negatív logikával.

6.1 táblázat. Az IM2 2 bites adder mikrocirkulusának igazságtáblája

Tekintsünk egy példát. Tegyük fel, hogy két számot kell hozzáadnunk a negatív logikához. Száma 5 pozitív logikával 0101 megfelel a bináris kódot, és negatív - 1010. A kódszám 7 megfelel a pozitív logika bináris kód 0111, és a negatív - kód 1000. Ha ezt alkalmazzuk, hogy a bemeneti kódot összeadó 1010 (decimális 10 pozitív logika), és 1000 (tizedes 8 pozitív logika) kapjuk a 10 + 8 = 18 összeget, vagyis a 10010 kódot a pozitív logikában. Mivel a carry bemenőjel C = 1 (nincs carry input a negatív logika), a kimenete az összeadó kódolni fogja egy nagyobb: 18 + 1 = 19, vagyis a 10011. A negatív logika akkor felel meg a száma 01100, azaz 12 hiányában carry kimeneti . Ennek eredményeként 5 + 7 = 12 volt.

Az összegző nemcsak az összeget, hanem a beviteli kódok különbségét is kiszámíthatja, vagyis kivonásként működik. Ehhez a kivont számot egyszerűen bitwise kell fordítani, és egyetlen jelet kell alkalmazni a C átviteli bemenetre (6.2. Ábra).

Ábra. 6.2. 4 számjegyű kivonó az IM6 adagolókon és az LN1 invertereken

Például számold ki a 11 (1011) és az 5 (0101) közötti különbséget. Bitenkénti invert száma 5 és megszerezni 1010, azaz a tizedes 10. Az összeadó 11, amikor foglalta így 21 és 10, azaz a bináris szám 10101. Ha a jel a C értéke 1, az eredmény 10110 elvetése az MSB (kimeneti jel P) és megkapjuk a különbséget 0110, azaz 6.

Egy másik példa. Legyen szükség a 12 (1100) és a 9 (1001) közötti különbség kiszámítására. 9 bitenkénti invert kapjunk 0110, azaz a tizedes 6. megtalálni a összesen 12 és 6, kapunk 18, és a C = 1, megkapjuk a 19., hogy egy bináris 10011. A négy darab legkisebb helyiértékű bitjére van 0011, vagyis egy decimális 3.

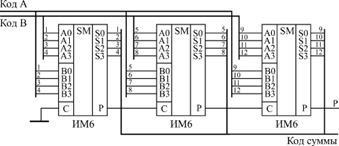

A bitmélység növelése érdekében nagyon egyszerű a lépcsőzetes adók. Szükséges egy jelet küldeni a legkevésbé fontos bitek feldolgozását végző adder átvitelének kimenetéről a legmagasabb számjegyeket feldolgozó adók átvitelének bemenetére (6.3 ábra). Amikor a három 4 bites tömörítő kombinálódik, egy 12 bites addzert kapunk, amely egy további 13-as számjegyet (a P transzfer kimenete) tartalmaz.

Ábra. 6.3. Az IM6 összeadók lépcsőzése a bit kapacitás növelése érdekében

Bizonytalan állapotok adódhatnak a beadók kimenetében bármelyik bemeneti kód megváltoztatásával (6.4. Ábra). Az összeg kimeneti kódja rövid időre olyan értékeket vehet fel, amelyek egyáltalán nem kapcsolódnak a beviteli kódokhoz, és az átvitel kimenetén rövid parazita impulzusok jelennek meg. Ennek oka elsősorban a bemeneti kódok bitjeinek nem egyidejű megváltoztatása. Annak elkerülése érdekében, hogy ezek a bizonytalan állapotok befolyásolják a további áramkört, szükség van a kimeneti jelek szinkronizálására vagy kapuzására. De ehhez információra van szükség a bemeneti kódok megváltoztatásának pillanataiban, ami nem mindig áll rendelkezésre.

Ábra. 6.4. Bizonytalan állapotok az adder kimenetein, amikor a bemeneti kódok megváltoznak

Az IM6 összegzõ késleltetése a bemenetektõl az összeg kimeneteire körülbelül kétszerese a logikai elem késleltetésének, és az átvitel kimenetétõl a kimenetig kb. 1,5-szer. Az IM3 additő késleltetése több, mint az IM6 fele. Ezért olyan rendszerekben, ahol a sebesség fontos, jobb az IM6 használata. Ez különösen akkor fontos, ha lépcsőzetesen növeli a bit kapacitását, mivel az egyes chipek késleltetése össze van kapcsolva. A késedelmek pontos nagyságát a referencia-könyvekben kell megvizsgálni.

Az aritmetikai-logikai eszköz olyan kombinációs típusú áramkör, amely nem igényel semmilyen időrel kapcsolatos órajelet működéséhez. A művelet eredménye az ALU kimenetén jelenik meg, miután az ALU belsejében a leghosszabb láncot képező logikai elemek késleltetéseinek késleltetése megegyezik. Az ALU bitek átvitelének egymás utáni áthaladása miatt a hosszabb lánc hosszának, és ezáltal az ALU teljes késésének hossza hosszának arányában növekszik. Nagyjából elmondható, hogy a 32 bites ALU késleltetése 32-szer nagyobb, mint az egybites ALU késleltetése. A speciális gyorsított átviteli rendszerek használata többszörös lehet a többszörös ALU késleltetésének csökkentésére.

Általánosságban a többfunkciós ALU egy működési részt (OS) és egy vezérlőegységet (CU) tartalmaz, amely végrehajtja a parancskód másodlagos dekódolását és meghatározza az ALU-ban végrehajtott műveletet.

4.2. Ábra. Az ALU felépítése

Az ALU-ban végzett műveleteknek funkcionális teljességgel kell rendelkezniük. A négy művelet funkcionális teljességének biztosítása:

- hozzáférés a memóriába adatok írásához / olvasásához;

- növekmény / csökkenés;

- összehasonlítás (felismeri a feltételes átruházás lehetőségét);

- állítsa le a készüléket.

Az első processzorokban a műveletek száma tizenhat évre korlátozódott, most több százra ér.

Az elvégzett műveletek száma az ALU egyik fontos jellemzője.

Az ALU az alább felsorolt jellemzők szerint osztályozható.

Az adatmegjelenítési módszer szerinti osztályozás:

- rögzített vesszővel;

- lebegő vesszővel.

2. Operandus szerinti operandus szerinti osztályozás:

· Egymást követő ALU, ahol minden egyes műveletet soronként hajtanak végre minden egyes számjegyen;

· Párhuzamos ALU, a művelet egyszerre történik az összes bit adaton;

· Az egymást követő párhuzamos ALU, ahol az adatszó szótagokra oszlik, az adatfeldolgozást párhuzamosan hajtják végre a szótag számjegyei és egymást követően a szótagok fölött.

3. A számrendszerek használatának osztályozása:

4. Az elemek és szerelvények használatának jellege szerinti osztályozás:

- blokk különálló számtani műveletek elvégzéséhez különleges blokkok kerülnek be az ALU struktúrába, amely lehetővé teszi az információfeldolgozási folyamatot párhuzamosan;

- szállítószalag ALU-művelet a csővezeték különböző szakaszaiban ugyanazon időközönként (órajel) végrehajtott mikro-műveletek sorozata, amely lehetővé teszi a műveletek végrehajtását az operandusok áramlásán minden óramutató ciklusban;

- A többfunkciós egységek univerzális ALU-k, amelyek számos műveletet végeznek egy eszközben. Ebben az ALU-ban a műveletet az opcode segítségével kell beállítani.

5. Idő szerinti osztályozás.

Az időjellemzők szerint az ALU-k a következőkre oszthatók:

- szinkron - a szinkron ALU-ban, minden művelet egy órai ciklusban történik.

- aszinkron - nem idõzített ALU, amely nagysebességû, mivel kombinációs áramkörökön történik.

6. A szabályozó szerkezete szerinti osztályozás: