képzés

Az egyik legfontosabb és legszélesebb körben használt digitális termékek egy számláló. Megpróbáljuk megérteni, mi a számláló, és hogyan kell építeni egy alapvető építőkövei a digitális áramkör. Átadás és kiegészítőt meg kell vizsgálni, mivel megkövetelik tőlünk, hogy hozzon létre egy szinkron számláló. Mi ez ellen, és mit hisz?

Meter funkció, mivel könnyen kitalálható, hogy megszámoljuk a impulzusok érkeznek a bemenetére. A munka megkezdése előtt a számláló alaphelyzetbe megfelelő jel (reset), és annak kimenete van beállítva, hogy az n-bites bináris kód egyenlő nullával. By aktív él az órajel a kód kimenete a számláló növekszik. Ezen túlmenően, a jelek is jelen lehetnek felbontás és számlálás iránya (csökkenése vagy növekedése a számláló értéke).

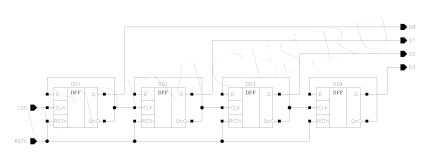

Mi már korábban tárgyalt hiányosságait aszinkron digitális áramkörök tervezése, de példaként én még szeretnék egy kiviteli alakját mutatja aszinkron számláló (feszültségingadozás számláló). Bár ez egyszerűbb, mint a szinkron számláló, és előírja a kisebb számú logikai elemek, ne használja a projektek! Ez tele van a hiba előfordulását a rendszerben, és akkor válhat oka megmagyarázhatatlan hibák. Az alábbi ábra a rendszer 4-bites aszinkron számlálót D-löket kiváltja:

Egy aszinkron számláló egy sorba kapcsolt kétütemű D-triggerek. Az aktív él az órajel (CLK) van megfordított állapotban az első flip-flop a láncban (LSB), t. E. A kimeneti változások 0-1, és fordítva. A órajelet minden ezt követő flip-flop vett kimenete az előző, így, minden ezt követő flip-flop kapcsolók 2-szer kisebb, előző (DD2 kapcsolva minden második órajelciklusban, DD3 - minden negyedik ciklus, stb ...). Ez a rendszer az aszinkron és a kimenő adatok frissülnek váltakozva legalább a folyosón a lánc indító jel.

A szerkezet valamivel bonyolultabb szinkron számláló. Emellett n kiváltó (n-bites regiszter), azt kell n-bites összeadó. Regisztráció tárolja a számlálási eredmény, és minden egyes órajel ciklus egy tárolt értéket kell hozzáadni egység (a vipera), és tárolja az új eredmény a nyilvántartásban. Mielőtt rátérnénk a végrehajtását egy ilyen számláló, meg kell érteni, hogy az összeadó és hogyan valósítható meg.

Vipera, mint a neve is mutatja, csak tovább növeli a két bináris számokat. Ezenkívül a bináris számok megegyezik a tizedes. A decimális aritmetikai álló számok 10 - 0 és 9 Ha hozzáadjuk a 9 egység, a kisülési túlcsordulás következik be (pozíció) szám és az egység átviteli fordul elő a következő mentesítési, így ha hozzáadunk 29 1, akkor az LSB túlfolyó, nem lenne 0, és a készülék át a következő számjegyre, és növeli annak értékét (2 + 1 = 3), kapjuk a 30. Hasonlóképpen, ugyanez a logika érvényes bináris számokat.

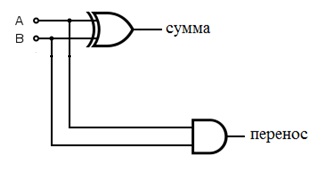

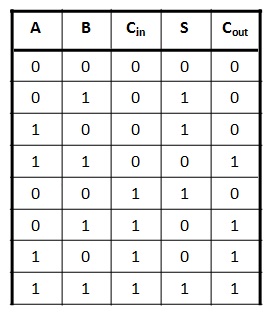

Kezdeni, hogy fontolja meg egy kicsit összeadó. Hogy került teszik logikai kapukat? Az egybites összeadó két bemenettel rendelkezik (a tagokból), és két kimenet - az összeg és végrehajtja a következő bit (túlcsordulás). Próbáljuk meghatározni, hogy melyik logikai függvény megegyezik az összeg kicsit, és carry bit. Nyilvánvaló, hogy az átutalást a következő számjegy (bit C - Carry) csak abban az esetben, ha a bemenet mindkét egység, az összeg bit értéke 0, mivel a mentesítés túlcsordulás történt. Kiderült, hogy az összeg a bitek nem más, mint az XOR kombináló bemenet (nézd meg a táblázatban az igazság XOR és nézd meg magad). Ebben az esetben a C jelentése átviteli bit logikai ÉS bemenet (a transzfer után csak akkor, amikor a két egység a bemeneti).

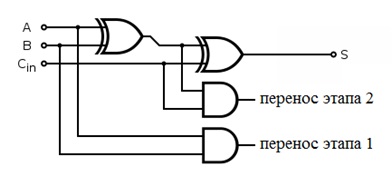

Ez a rendszer az úgynevezett fél-összeadó, mert nem veszi figyelembe a carry bit az előző mentesítés, bár önmaga hozza létre a carry a következő számjegyre. Annak érdekében, hogy transzfer egy előző szakaszban hozzá kell adni az összege az A és B is átviteli bit az előző lépésben, azaz, hogy egy második fél-összeadó:

Így, ha az átutalás alakult legalább az egyik fél összeadó, meg fog jelenni a termelés a teljes összeadó. Ehhez alkalmazza a logikai VAGY.

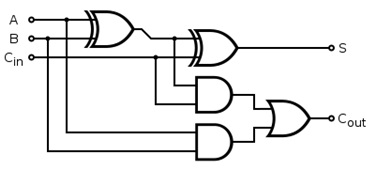

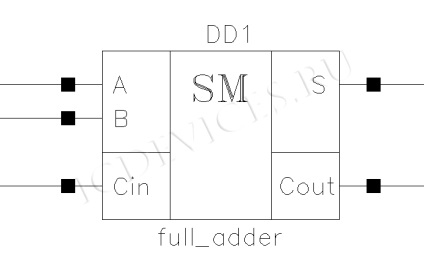

Egybites teljes összeadó három bemenettel (kettő bit amelyekhez hozzá kell adni az e mentesítési és a carry bit az előző szakasz) és két kimenettel (az összeg bit és a carry bit a következő bit).

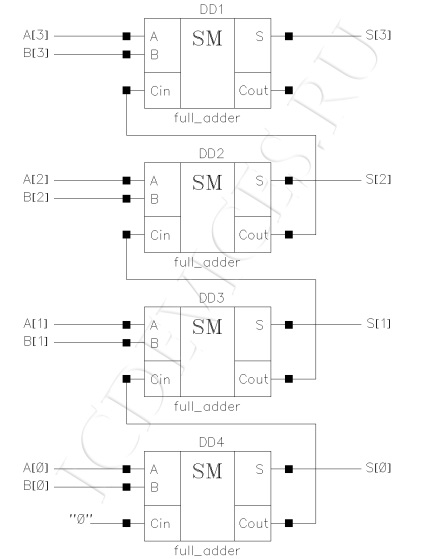

Megvalósítása n-bites összeadó, akkor n teljes kiegészítőket. Ahhoz, hogy a bemenetek és B szállítjuk megfelelő biteket számok kell hajtani, és minden egyes bitje bemeneti Cin kimenetére csatlakoztatott az előző mentesítési Cout, Cin és a bemeneti a LSB tápláljuk log. 0. Az alábbi diagram 4-bites összeadó ([0] - LSB, [3] - MSB):

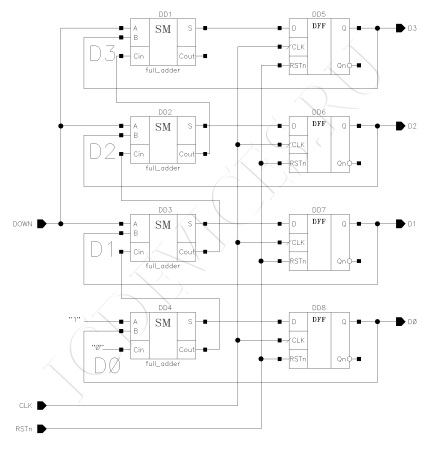

Ezzel minden készen áll a végrehajtásához szinkron számláló. Bit bonyolítja a problémát, és egy számlálót, amely gól az előre és hátrafelé. Vezessen be további bit számlálási irány és ha 0 - növeli egy-egy órajel ciklus, és ha egyenlő 1 - elvesz egy minden órajel ciklusban. Azzal a kiegészítéssel, világos, de elvesz egy? Vonjuk egyik szám megegyezik, hogy hozzáadjuk a szám a „mínusz egy.” Bináris számok egy jel képviselteti magát az úgynevezett kiegészítő kódot. Ahhoz, hogy a bináris ábrázolása egy negatív szám, meg kell fordítsa a bitek és a hozzá egyet rá. Például a 4-jegyű számot az „5” bináris formában néz ki, mint 0101, így a szám „-5” inverz bit - megszerzése 1010 és hozzáad egyet - kap az 1011. Most, ha hozzátesszük, ezek a számok 5 és -5, akkor azt kapjuk: 0101+ 1011 = 10000, a túlcsordulás következik be, az egység menni a következő számjegy, de nem tartja (ez a bit „dobni”). Mivel mi már össze a 4-bites számok, a kimenet is csak a 4 LSB, azaz 0000. Meg kell jegyezni, hogy a kiegészítő kód MSB meghatározza a jel .. (Unit - a jele negatív szám). Ezáltal a közvetlen kódot 4-bites számot lehet képviseli decimális szám 0 és 15, valamint a fordított kódját -8 7.

Tehát folytassa a végrehajtását 4-bites szinkron számlálót. A számláló három bemenettel: órajelet, a számolás irányát, és a reset jel (reset). Az aktuális számláló értéket tárolja a regiszter (4-ütemű D-flip-flop). A regiszter kimeneti áram számlálási érték érkezik összeadó bemenetet (pl bemenet B). A másik bemenete a összeadó (A) megkapja a értéke „1” (0001) vagy a „-1” (1111) függően a számolás irányát. Úgy tűnik, a kimeneti összeadó új értéket növelni vagy csökkenteni egy, ami jut a nyilvántartásban bemenet. By aktív él az órajel az érték a nyilvántartásban tárolt és a kimenet a számláló frissül.

Ha DOWN = 0, akkor a bemenet összeadó 0001 megkapja a számot (plusz egy), egyébként (LE = 1) a menetek száma 1111 (kivon egy) bemenet összeadó. Megjegyezzük, hogy az összes flip-flop órajele csak jel CLK. és az összes bit a számláló frissülnek ugyanakkor az aktív él az órajel. Fontos megérteni, hogy az új adatokat, mielőtt a következő aktív él CLK (összeadó késleltetés nem haladhatja meg az időszak az órajel) helyes működését az áramkör kimenetén az összeadó időt kell hagyni jelenik meg.

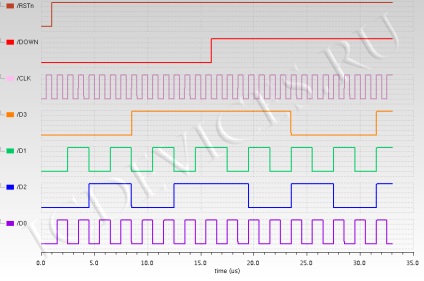

Idődiagram számláló jeleket (a számláló nullázódik az alacsony szintű jel RSTn bizonyít «n» utótag.):

Itt egy egyszerű szinkron számláló. Ezután próbálja leírni a Verilog nyelv és megismerkedhetnek a környezetet a ModelSim szimuláció.