Számtani eszközök

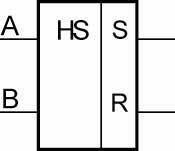

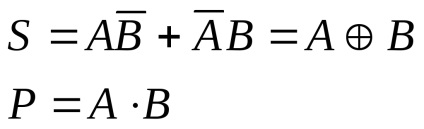

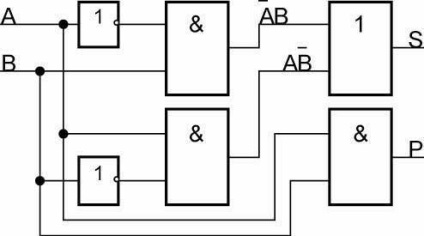

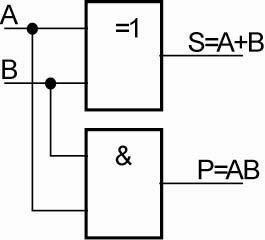

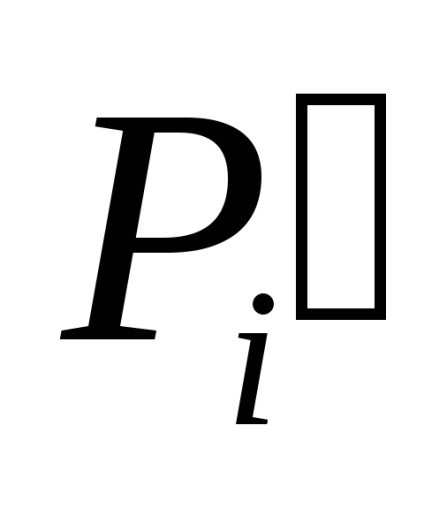

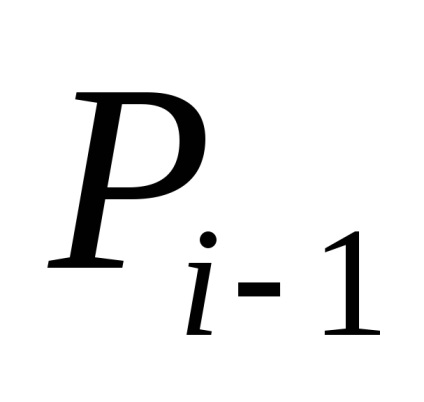

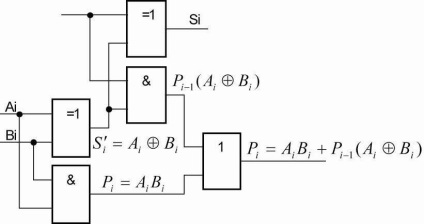

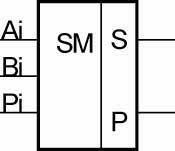

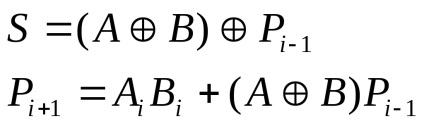

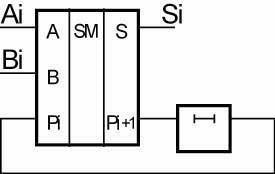

A féladagoló működését az alábbi egyenlet írja le:

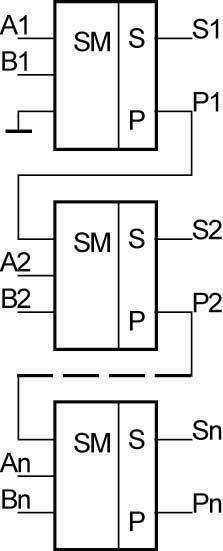

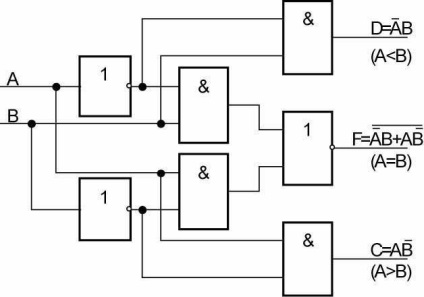

A féladagoló logikai szerkezete általános és kiterjesztett formában

A HS két bemenettel rendelkezik, ezért csak kis sorrendben használható. A két többszörös számozású számjegy összegzéséhez a második számjegyből kiindulva három bemenetre van szükség: kettő a summandumok számára

A teljes összeadódást két félösszegző egységként lehet ábrázolni. Az egyik egy kategóriába tartozó két szám beillesztését szolgálja, és egy köztes mennyiség kimenetét biztosítja

A szekvenciális bemeneteknél az összes számjegy közös egy teljes adder, további késleltetési áramkörrel. Mindkét kifejezést impulzus szekvenciák kódolják, amelyek szinkronban bemennek az A és B bemeneteken keresztül

n

Méltóság - kis hardver költségek.

A hátrány viszonylag alacsony sebesség.

Az egymást követő hordozós n-bites párhuzamos függő többrészek száma megegyezik a számjegyek számával.

A

A feltételek

A sebességet az átviteli késleltetés korlátozza, amíg a legkevésbé lényeges bitből a továbbítási jelet el nem terjesztik az egész rendszerben.

Az átviteli idő csökkenti a párhuzamos szállítás bevezetését, amelyet a gyorsított (átadott) blokkok bevezetésével valósítanak meg.

Minden egyes bithez két további jel van:

A gyorsított átvitel folyamatát az alábbi egyenletek írják le:

Digitális komparátorok (komparátorok)

A digitális összehasonlítók (összehasonlítás összehasonlítása) két számot hasonlít össze bináris (bináris-tizedes) kóddal.

Attól függően, hogy a áramköri megvalósításának komparátorok tudja határozni az egyenlőség vagy egyenlőtlenség: A = B, A> Bilia> B, gdeAiB- független számok azonos számú bitet. Az összehasonlítás eredménye a kimenet logikai szintjeinek megfelelően jelenik meg.

A digitális komparátor chipek általában ezeket a műveleteket végzik, és három kimenettel rendelkeznek.

Megtalálni a megfelelő számot (szót) a digitális információ streamjében.

Az óra elteltével az óra.

A feltételes átmenetek végrehajtása számítástechnikai eszközökben.

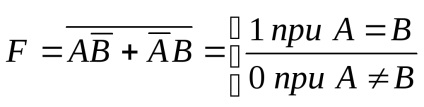

Egyszámjegyű komparátorként logikai áramkör használható, amely az ekvivalencia műveletet hajtja végre (exkluzív OR-NOT). Leggyakrabban az "exkluzív - OR" alapján épül fel.

Az egybites komparátor kibővített logikai szerkezete a következőképpen alakul:

az A> B (azaz A = 1, B = 0)

az A<В (т.е А=0, В=1)

Két n-bites bináris szám egyenlő, ha a párok egyenlő az összes számjegy ezeket a számokat. Ha chislaAiB- négyjegyű, a jele egyenlőség: A3 = B3; A2 = B2; A1 „= B1; A0 = B0, Ilia = BpriF = F3F2F1F0 = 1, esliF = 0, TOA ≠ B.

Az A> B egyenlőtlenség a négy esetben egyike:

A3 = B3; A2 = B2; A1> B1;

A3 = B3; A2 = B2; A1 = B1; A0> B0.

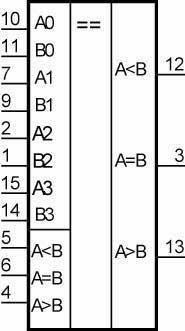

Egy digitális összehasonlító példa az IS K561IIP2.

A chipnek bővíthető bemenetei vannak, amelyek lehetővé teszik mindkét szám digitális kapacitásának növelését további logikai elemek nélkül. (A = B, A> B, A> B)

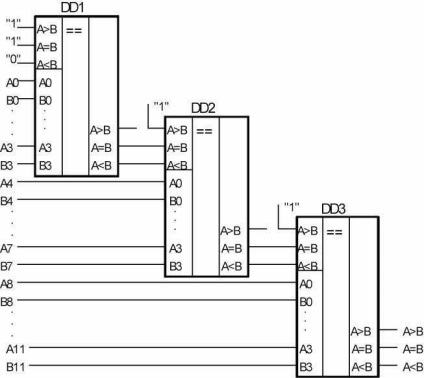

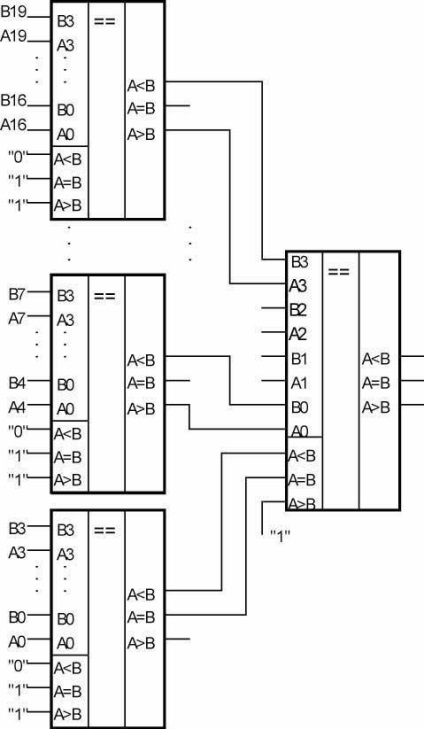

A komparátorok kaszkádszerűen és párhuzamosan csatlakoztathatók.

Párhuzamos (piramisos) kapcsolat esetén a késleltetési idő rövidebb (azaz a komparátorok sebessége magasabb.)

A digitális komparátorok lépcsőzése:

Kimenetek A = B és A

Ez a művelet javítja a bináris információ továbbítás megbízhatóságát.

A hibák kimutatásának egyszerű és hatékony módja azon a feltételezésen alapul, hogy minden egyes időpontban a hiba csak egy számjegyben fordulhat elő, és egy egységben vagy egy egység veszteségében nyilvánul meg.

Így. ha az átvitt szó minden számjegy számára egyenlő számú számot tartalmaz, és az átviteli vonal végén ez a szám páratlan, akkor hiba történt.

Ez a módszer speciális paritássémák alkalmazásával valósul meg.

Az előző elem kimenetén lévő információ alapján az áramkör egy további bitet (paritás vagy referencia bit), azaz "1" vagy "0" -ot generál, amely hozzáadódik a kimeneti információhoz.

Paritásbit hozzárendelése - az egyes átvitt szóban lévő egységek számának egyenlő vagy páratlan, az elfogadott kódolási rendszertől függően.

A vonal fogadó végén egy paritásellenőrzést végeznek. Ha helyes, a vétel engedélyezett, ha nem, a hibajelző bekapcsolt állapotban van.

A paritás egyenletes és furcsa lehet.

Furcsa paritás esetén az egységek összege, a vezérlőbitnek együttesen páratlannak kell lenniük, az egyenlő bit pedig az ellenkezője. A gyakorlatban a páratlan paritást gyakrabban használják, mivel a páratlan ellenőrzés lehetővé teszi a teljes adatvesztést.

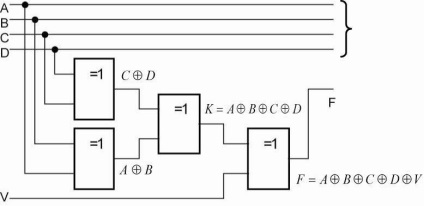

A paritásellenőrzési rendszer szerkezete többlépcsős. Az első szakaszban (sorozatban) a szó összes bitjét párban összegezzük. Az első szint kimenő jelei a másodikhoz kerülnek, és így tovább, egészen a teljes szó paritásának vagy páratlanságának meghatározásáig.

Az utolsó fázisban kapott eredményt összehasonlítjuk egy vezérlőjellel, amely meghatározza a használt paritás típusát.

Ha paritás páros, r. E. száma is egy szó, beleértve a paritás bit egyenletesnek kell lennie, a vezérlő jel legyen összegével egyenlő modulo 2 összes információ bitek a szó. A páratlan paritás ellenőrző jel inverzét említett összeget.

Vagyis, függetlenül a négybites ABCD szó egyenlõségétõl, az ABCDF ötjegyû kód egyenlõsége mindig azonos lesz.

A bemeneti potenciál határozza meg a használt paritás típusát.

A független termékekre példa a CMOS IS K561SA1 és a TTL K155IP2.