Memory Interface Controller Architecture Sram a maximális teljesítmény

ÉPÍTÉSZET vezérlő interfész SRAM memória a maximális teljesítményt a kapcsoló készülék

Kutató Intézet Rendszer Tanulmányok RAS, ***** @ *** niisi. *****

A kapcsolók, épül alapján a switch, a leggyorsabb módja annak, hogy kölcsönhatásba port. Ez a kapcsolat jön létre a switch port és a cél megkapja port, amelyen keresztül az adatátvitel. Ha a cél port foglalt, az adatok pufferelt a CPU bemeneti portot. A kapcsolók a közös busz portok processzorok kapcsolódó nagy sebességű busz. A hátránya ezeknek architektúrák az, hogy nincs kapcsoló mátrix, vagy a közös busz nem teszi lehetővé adatok pufferelésére.

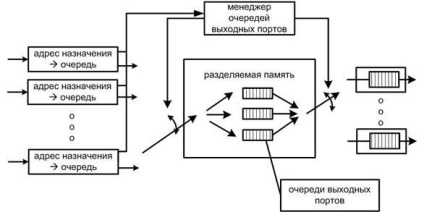

Kapcsolók osztott memória olyan memória használatával tárolására szolgáló egység a tárcsát váró adatok kiszámításához az útvonal és / vagy a cél port kiadás (ábra. 1).

Ábra. 1. Váltson a megosztott memória

Bemeneti portok processzor egység van csatlakoztatva egy átkapcsolható bemeneti osztott memóriát, és a kimeneti egység a feldolgozók is csatlakozik a kapcsolt kimenet az ezt a memóriát. A bemeneti és kimeneti vezérlők a megosztott memóriát kimeneti port sorkezelőnek. Egy ilyen kapcsoló van egy magasabb adatátviteli késés, de kevesebb az adatvesztést. Az ilyen kapcsolók, adatfeldolgozó oszlik három fő lépésből áll:

· Fogadása adatok - a bemeneti portok a feldolgozók rögzíti a beérkező adatcsomagok az osztott memóriában;

Termelékenység memória, ha egy ilyen építészeti különleges követelmények. Memory kell elegendő sávszélességet a bejövő portokat, hogy hozzáférjen a memória adatok rögzítésére veszteség nélkül; míg a kimeneti portok ideje elolvasni, hogy ne szakítsa meg az adatokat továbbították, szerdán vége előtt a blokk. Azaz, a memória kapacitása többszöröse a kapacitás az egyes csatornán. Tekintsük a memóriaigénye 6 portos switch a Gigabit Ethernet. Minden port működik full duplex üzemmódban egyszerre fogad és továbbít adatokat a sebessége 1 Gbit / s. Azaz, a memória biztosítani kell egy kapacitása 12 Gbit / s.

Az ilyen rendszerekben a statikus memória SRAM. Ez a memória egy egyszerű felület, bár a költség magasabb. A legrosszabb esetben 12 switch portok fordul tetszőleges memória helyet adat írására és olvasására igénylő további aktiválás ciklusok és záró vonalak és regenerációs ciklus. Ha DRAM komponensek pipeline adatfeldolgozó, kapcsolási késleltetést bármelyike között a sorok 2 ciklus hossza a adatcsomag 4 ciklusban. Ezzel a művelettel dinamikus memória, amely a kívánt kapcsolót teljesítmény lenne szükség nagyobb működési frekvenciák képest SRAM statikus memóriát.

Helyezzünk egy blokk memória SRAM a switch chip drága fejleszteni / vásárlás SRAM nagysebességű memória blokk, és magas követelményeket támaszt a termelés a chip, különösen megköveteli a technikák kombinációját hétköznapi logika és tárolása nagy mennyiségű (a switch használt memória kapacitása 4 MB) . Egy külső SRAM memória chip csökkenti ezeket a költségeket, de ehhez cella helyét az áramköri lapon a rendszerben használt. switch chip használatra tervezték egy külső memória SRAM.

Hagyományos SRAM típusú memória chip egy 32-bites port olvasási / írási működő 200 MHz, kihagyja 6,4 GB adatot másodpercenként, azaz biztosítja Job 3 port. Ahhoz, hogy hozzon létre egy 6 portos switch szükséges kapacitásának növelése a memória két alkalommal. Ez megköveteli a használatát egy ilyen emlékek:

· Egy 32-bites kettős port memória működik 200 MHz;

· Egy 64-bites memóriában működő 200 MHz;

· DDR memória (dupla adatsebességű) 200 MHz-en;

· Egy-port 32-bites memória 400 MHz térerővel működő.

Mindezek a megközelítések megvannak az előnyei és hátrányai:

· A használata a DPRAM memória döntőbíró leegyszerűsíti a műveletet (működő nagyfrekvenciás), amelyek most szükség, hogy nyomon követi és kezeli fél kérelmeit, de ugyanakkor növeli a kimenőjel a chip. Ebben a kettős port memória lehet „igaz” dual-port, ahol minden csatlakozó memória működik az olvasás és írás, vagy „egyszerű” dual-port memória, amikor az egyik port csak olvasható, és a második - csak a rekordokat. A kapcsoló eszköz írni és olvasni kéréseket egyenlően osztják, és ez a felosztás a funkcionalitás memória portok jelentéktelen; más eszközök, például memória kell megválasztani, figyelembe véve a követelményeket a projekt.

· Válogatás a memória chip, órajele 400 MHz, vagy használatát DDR memória társul technikai nehézségek, mert a design nemcsak a belső logikai egység üzemelésre alkalmas 400 MHz (ami befolyásolja a tervezés időpontjában és használata technológia), hanem sokkal bonyolultabb NYÁK tervezés, a rendszerben alkalmazott. DDR memória igényel egy kis változás a rendszer a munkát a DMA-vezérlő.

A legjobb módszer a fejlesztés az arány a komplexitás / költség, hogy növelje az adatbusz szélességét. Ebben az esetben az egyik kapcsoló rendelkezik egy 64 bites hozzáférés a memória csatorna olvasási / írási, órajele 200 MHz (összesen 12,8 Gbit / s), és 6 által képviselt a kapcsoló portok segítségével 12 memória-hozzáférést csatornák (olvasásra és írásra ). DMA-vezérlő kezeli a kérelmeket a switch portok memória-hozzáférést és az időszerű és folyamatos adatfolyamot.

Annak érdekében, hogy alacsony költségű a fejlődés, meg kell váltani a mag chip működik egy kisebb gyakorisággal - 50-100 MHz. Ezek a frekvenciák használatával érhetőek el a számítógéppel segített tervezés rendszer sokkal kevesebb erőfeszítést 200-250 MHz, hogy a projektgazdától időigényes vagy drágább gyártási technológiával készült.

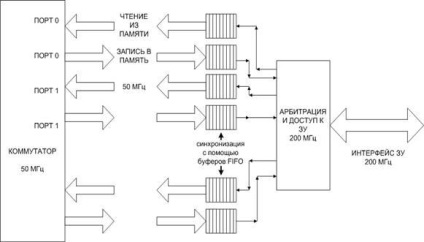

Azt javasoljuk, hogy a memória interfész vezérlő architektúra (2. ábra)

· Memória interfész egység működés a kívánt magas gyakoriságát memória-hozzáférés (200-250 MHz);

· „Belső” vonatkozásában a kapcsoló memória interfészek működő közepes / kívánt gyakorisága 50-100 MHz;

· Pufferek szinkronizálás és lapozó a kötődése a két interfész.

Single-port SRAM memóriát igényel arbitratsii csatornák között 12 lekéréssel. Az egyenletes eloszlását hozzáférési portok memória legalkalmasabb ciklikus forgalmazás (Round-Robin ütemezés). Lehet a vezetékes és végrehajtani több ciklusban, hogy elérjék a kívánt sebességet arbitratsii, blokk munka. Így csökkenti a ráfordított idő memória-hozzáférés olvasási / írási művelet célszerűen szakaszos üzemmódban, amikor megkapta a memória hozzáférés egy csatorna egymás olvas / ír egy szót sem. Ugyanakkor, csomag mérete ne legyen túl nagy, úgyhogy rögzít vagy olvas egy csatorna nem blokkolja a munkát a többi csatlakozástól. Ebben a vizsgálatban hozzáférésű memória végre egy csomag mérete négy 64 bites szó.

Ábra. 2. Az áramkör a DMA-vezérlő

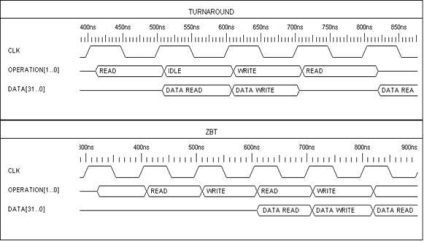

A hálózati technológiákat igénylő nagysebességű hozzáférés a memória a piacon memóriával ZBT® / NOBL ™ SRAM (Zero Bus átfutási - nulla busz kapcsolási ciklus, nincs busz várakozási idő - hiányzik a busz késleltetés). Ez a memória maximális sávszélessége megszüntetésével a kapcsolási ciklus közötti olvasási és az írási (4.). ZBT® SRAM memória eszközök működnek mind streaming és anyagmozgató berendezésekkel. Szállító eszközök működnek a magasabb frekvenciákon és kisebb adatfolyam késés.

A legtöbb gyártó készít SRAM memória továbbfejlesztett adatbusz, amely lehetővé teszi olvasni és írni az extra bitek byte-paritás (18/36 bites adatbusz). Amikor két memória chipek egy 36 bites párhuzamos busz, álló további 8 bit használatát teszik lehetővé redundáns kódok hibák feltárására és kijavítására. Például a Hamming-kód segítségével korrigálni egybites hibák az adat buszon és hibákat két bit. 32 bit adat Hamming-kód használ további 7 bit 64 bit - 8 bit. Coding / hibajavítás előtt közvetlen memória-hozzáférés, hogy ne növekedjen a szélessége a puffer szinkronizálást. Szállító arbitratsii munka memóriakérést egység lehetővé teszi a vezetékes is viszonylag lassú blokk kódolást / Hamming igénylő kizárólagos VAGY műveletet az adatbusz 64 bit. Így a kapcsoló érjük transzparens a hibák kijavítását.

A javasolt architektúra a következő tulajdonságokkal rendelkezik:

· Két memória chipek párhuzamosan telepíthető, így a szükséges sávszélesség.

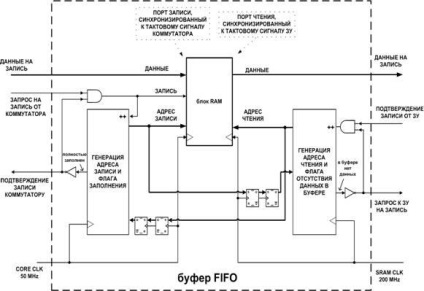

· Adatszinkronizációs különböző óratartományába a FIFO puffer.

· Kötegelt feldolgozás érdekében, hogy csökkentsék a hozzáférési idő / arbitratsii.

· FIX bithiba / hibák feltárása két bitet használ Hamming-kódot.

Ábra. 3. FIFO puffer a levelet adatokat a memóriából

A bemutatott megoldás a memória maximális teljesítmény összetevő SRAM. Ahhoz, hogy egy kapcsoló több portot vagy a technológia támogatja a gyorsabb (gyorsabb, mint 1 Gb / s) van szükség, hogy tovább növelje a kapacitást a csatorna memória-hozzáférések. Ebben az esetben az alkalmazott megközelítések nem lehet alkalmas, és a legvalószínűbb megoldás látható, hogy egy külső memória típusa DDR (II) SDRAM, amelynek nagyobb az üzemi frekvencia (SRAM limit 300 MHz), illetve az egyéb chip gyártási technológiák, hogy keresse meg a megosztott memóriát a kapcsoló chip .

Ábra. 4. A szinkron memória nulla kapcsolási ciklus képest

hagyományos memória

A cikk bemutatja a architektúra a memória interfész vezérlő, amely biztosítja a maximális használata a SRAM, miközben viszonylag alacsony frekvencia működését Switch IC mag. Ez az architektúra biztosítja a szükséges folyamatos hozzáférést több Gigabit switch csatornákat a memóriát és csökkenti a költségeit a SRAM memória chipek és RF tervezéstől a memória hozzáférési felületet.

1. Olifer hálózat. Elvek, technológiák, protokollok. - SPb. Peter, 20c. il.

2. ISO 35,100 szabvány - Nyílt rendszerek összekapcsolása // www. iso. org.

6. Altera Stratix Device Handbook, Altera Corporation.