Avr dolgozó külső memória i2c eeprom típusa 24cxx, nagits - s blog

Annak érdekében, hogy teljes mértékben megértsék a két-Wire interfész (TWI). levelet a nulláról AVR STUDIO inicializálási eljárást, olvasás és írás. Laknak minden egyes lépésnél foglalkozik. Ezután modellezésére minden Proteus.

Hardver modul TWI és I2C protokollal

A MEGA Series MCU közé TWI modul, amely együtt fog működni a I2C busz. TWI modul lényegében közötti közvetítő a programot, és a csatlakoztató eszköz (memória I2C EEPROM, például).

A szerkezet a TWI modul AVR mikrokontrollerek

I2C busz két vezetéket:

- SCL (soros órajel) - sorban a soros órajel.

- SDA (Serial Data Line) - line soros adat.

Ez a busz tudunk egyszerre csatlakoztatható akár 128 zsetont.

Kapcsolatok a busz TWI

Amint látható a folyamatábra, TWI hagyományosan négy blokk. először is meg kell felállítani generátor kapcsolat sebessége, és mi is feledkezhet róla. A fő munka - a vezérlőegység.

Tehát a feladat most, hogy foglalkozik a nyilvántartások tartozó generátor kapcsolat sebessége és vezérlő egység:

sebességű kommunikációs regiszter TWBR

Control Register TWCR

állapot regiszter (állami) TWSR

adat regiszter TWDR

És mindez csupán érteni 4 nyilvántartások, képesek leszünk együttműködni a külső EEPROM és általában kommunikálhat I2C más eszközzel.

Generátor kommunikáció sebessége és a kommunikáció sebességét nyilvántartásban TWBR

sebességű generátor egység vezérli a kommunikációs vonal SCL, azaz az időszak órajelek. Kezelése az SCL csak vezethet. SCL időszak vezérli a kommunikációs sebesség beállítás regisztrációhoz TWI (TWBR) és bit előosztóval TWI állapot regiszter (TWSR).

SCL frekvencia keletkezik szerint a következő képlet:

- TWBR - érték a nyilvántartásba TWI kommunikációs sebesség;

- TWPS - bit előosztóval érték az állapot terül TWI (TWSR).

- Ftspu - mester órajel frekvencia

- FSCL - frekvencia óra SCL-

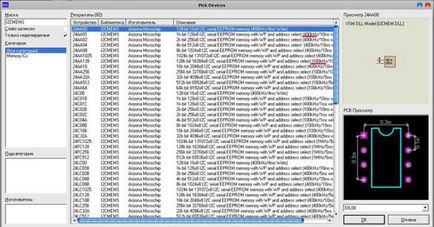

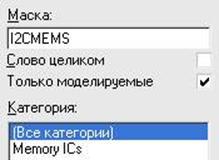

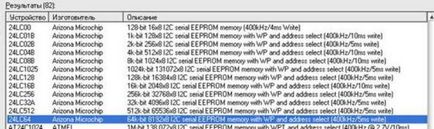

Beállítás TWBR szükség, mert led chip képzett kommunikálni egy adott frekvenciát. Például a Proteus, írja be a keresési I2CMEM, látni fogja a rengeteg memória chipek, többnyire a frekvenciák 100 és 400 kHz.

Nos, ebben az esetben a képlet és frekvencia FTSPU FSCL. találunk egy optimális érték TWBR nyilvántartásba.

TWPS - Ez egy 2 bites szám [TWPS1: TWPS0], az első bit - mentesíti TWPS0 második - TWPS1 TWSR a státusz regiszterben. Megadása előosztóval 4 TWPS kommunikáció sebességét. tudjuk alacsonyabb az érték TWBR (mint TWBR - egy bájt, a maximális értéke 255). Ez azonban általában nem szükséges, így TWPS, jellegzetesen 0 és 4 TWPS = 1. Sokszor nem, éppen ellenkezőleg, ütközünk az alsó tartományban TWBR nyilvántartásba. Ha TWI működik Master módban, akkor TWBR értéke nem lehet kevesebb, mint 10. Ha TWBR érték kevesebb, mint 10, a busz master eszköz generál téves jeleket az SDA és SCL vonalak továbbítása során bájt.

7. osztály - TWINT: TWI Interrupt Flag

Ez a jelző a hardver, ha az aktuális feladat befejezése TWI (például adások kapott adatok), és várja a választ a program. SCL vonal marad az alacsony állapotban marad, amíg a jelző TWINT. TWINT Flag törölhető program írásával bele a logikai 1-tisztítása ez a zászló okoz TWI újbóli működését, azaz A szoftver reset a zászló kell végezni befejezése után lekérdezési állapot nyilvántartások és TWSR TWDR adatokat.

6. osztály - TWEA: Bit felbontású megerősítés

TWEA bit vezérli a generáció a megerősítő impulzust. Amint a táblázatban látható, alapértelmezés szerint nem törli. Laknak akkor nem, akkor ebben a cikkben nem praktikus.

Az 5. melléklet - TWSTA: Bit START feltétel

Meg kell beállítani ezt kicsit, ha szükséges lesz a vezető az I2C buszon. TWI hardver ellenőrzése a rendelkezésre álló busz, és létrehoz egy START feltételt, ha a busz szabad. Mi ellenőrizze a feltétel (a státusz regiszter lesz), és ha a busz szabad, akkor lehet kezdeni dolgozni vele. Ellenkező esetben meg kell várni, amíg a busz szabad.

4. melléklet - TWSTO: Bit STOP feltételek

Telepítés TWSTO kicsit a mester mód eredménye ismét I2C STOP feltételt a buszon. Ha gumiabroncsok állapota STOP bit TWSTO automatikusan törlődik, és a gumiabroncs felszabadul.

Grade 3 - TWWC: Flag hibás bejegyzés

TWWC bit be van állítva, amikor egy kísérlet arra, hogy adatokat írjon be a nyilvántartásba TWDR amikor TWINT alacsony. A zászló törlődik a nyilvántartás írási TWDR amikor TWINT = 1.

Grade 2 - twen: Bit művelet lehetővé TWI

Bit twen lehetővé TWI működését és aktiválja a TWI felületen. Twen Ha a bit be van állítva, a TWI feltételezi az input-output vonal funkció SCL és SDA. Ha ez a bit nulla, a TWI van tiltva, és minden transzferek megszűnik állapotától függetlenül működik.

Bit 1 - fenntartott bit

Byte 0 - TWIE: Felbontás TWI szakítsa

Ha ez a bit rögzített naplót. 1 bit be van állítva a regisztrálnom sreg (globális megszakítás engedélyezve van), majd hagyjuk megszakítani TWI modul (ISR (TWI_vect)) bármilyen változás a státusz regiszter.

Állapot regisztrációhoz TWI - TWSR

Az adó üzemmódban TWDR nyilvántartásban bájt továbbítására. A vevő üzemmódban regisztrálja TWDR tartalmazza az utolsó fogadott byte. Legyen óvatos, a hardver telepítés TWINT zászló, TWDR nyilvántartás nem tartalmaz semmi konkrét.

Minden funkció (inicializálás a TWI, olvasni, írni a külső memória) tettem külön fájlokban, hiszen beleegyeztek abba, i2c_eeprom.c és i2c_eeprom.h.

Nos, a legfontosabb funkciója írtunk. Ezen az alapon, akkor írj egy függvény olvasni egy sor bejegyzés \ bájt. Az is lehetséges, hogy adjunk egy megszakítás ISR (TWI_INT), amely akkor lép működésbe, minden változás a státusz regiszter. Én csak néhány szót erről, mert miután megértette a fenti, akkor nem lesz nehéz megvalósítani őket magad.

lesz a következő kódrészletet viselünk a ciklusban:

A folyamat az olvasás a változások lesz egy kicsit bonyolultabb, mert olvasott adatok közötti byte kell igazolás a mester, és miután elolvasta az utolsó bájt megerősítés nem kell, majd a feltétele az átvitel befejezéséig (feltétel STOP).

Mintegy megszakítás ISR (TWI_INT) nem mond semmit, csak egy példát használ (ez általában elég, ha világossá válik minden):

Minden, ami marad, hogy hozzon létre egy projektet AVR STUDIO:

A projekt beállításai határozzák bármely MEGA (atmega16 példa), és csatlakoztassa i2c_eeprom.c i2c_eeprom.h fájlokat.

A programban azt egyértelműen az én vezérlő órajel 16 MHz-es. Továbbá, a Proteus, akkor válasszon ki néhány külső memória chip I2C EEPROM. Ne felejtsük el, majd összehasonlítani a beállításokat i2c_eeprom.h a paramétereket a kiválasztott chip (slaveF_SCL slaveAddressConst -. Megbízható információk mindig megtalálhatók a adatlapokon).

Így továbbra is építeni a projekt, és folytassa a modellezés ..

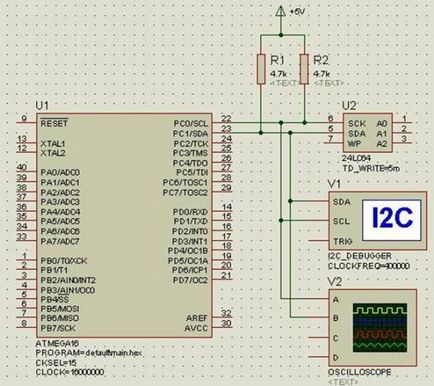

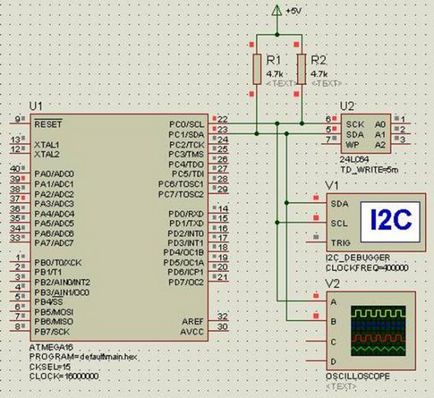

III. Szimuláljuk dolgozik I2C EEPROM Proteus

Hozzátéve, hogy ATmega16 2. kör pullup ellenálláson I2C busz (lásd. A rendszer az elején). Lapjairól virtuális eszközök és vegye oszcilloszkóp I2C-debugger. Válassza ki a memória típusa a keresési I2CMEMS eszközök kiválasztása képernyőre:

A teljes listát 24LC64 kiválasztottam egy memória kapacitása 64 KB és gyakorisága I2C busz 400 kHz.

A beállítás a vezérlő adja meg a firmware órajel 16 MHz-es és nem szabad elfelejteni, hogy hozzanak CKSEL-Fyuz a kristályt. Az I2C-hibakereső beállításokat jelzik, hogy a busz órajelek 400 kHz.

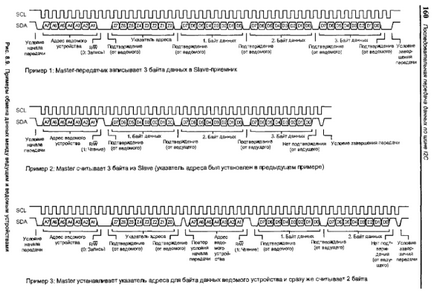

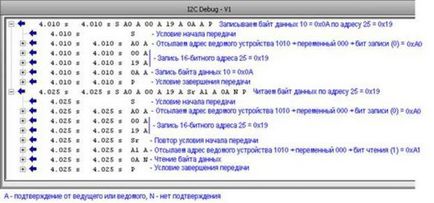

Most már megy le egy másik szint alá, és nézd meg a hullámforma:

[4] Microchip 24AA64 / 24LC64 adatlap

Valami nem vagyok skopipastil.