Belső eszköz plsis (fpga)

A közelmúltban, a jól ismert kínai site kínál vásárolni mindenféle sonkák értékelő táblák az FPGA. de sajnos, ami elérhető a felkészületlen elme (vagy az egyik, hogy kellemes lesz nekem) leírása orosz (Hogyan is működik ez?) az interneten, nem találtam. Végül, természetesen, a megértés, de ez is egyfajta, és a vágy, hogy írjon egy bevezető cikket gyönyörű képek, amelyek egyértelműen kifejtette a lényege az FPGA. Kezdjük.

FPGA - programozható logikai integrált rendszer. FONTOS! Kétféle LSI (Large Integrated Circuit), amely már a FÁK felel meg az FPGA, de mégis, a működési elve az LSI különbözik, amely létrehoz néhány disszonancia az igazi dolgok állása. Ugyanakkor a nyugati minden LSI-k váltották meglehetősen saját nevében, világosan tömörítő dot az i, nevezetesen: CPLD-chip - egy FPGA firmware (konfiguráció) mindig tárolva van a chip is, és a készülék ki van kapcsolva SOHA törlődik. Úgy tűnik, elég logikus, hogy az önálló piercing kell tárolni a chip, és összpontosítani, hogy ne legyen, de lépni a következő LSI. Az FPGA-chip is FPGA, de a konfiguráció egy külső, nem-felejtő memóriaforráson (pl. Mindenféle flash) tárolódik. Hogyan működik? Nagyon egyszerűen, minden alkalommal, amikor bekapcsolja, az FPGA konfiguráció varr magának, amelyet ki kell venni a memóriát és törlődik, ha kikapcsolja.

Meg kell jegyezni, hogy az írás folyamata a konfigurációs CPLD és FPGA nem különbözik: a leírásból nyelv VHDL hardver vagy Verilog. Aztán ott van a szintézis és végrehajtása (a fordító először próbálja megérteni, hogy mit írt, majd megpróbálja elhelyezni minden szerkezetet, regiszterek és a kapcsolatok az FPGA, írásbeli alapján), és az utolsó szakaszban keletkezik .bit - fájl varrott JTAG programozó interfész a készülékben.

Ha CPLD mégis valahogy szokott dolgozni ( „Nos, hogy a mikrokontroller!” - mondom), akkor az FPGA, annak érthetetlen külső memória források, úgy tűnik, hogy néhány kínos fenevad, így minden alább írva kell szentelni az FPGA (de trükkök a programozás a CPLD-re is érvényes) annak tisztázása érdekében. Minden kódmintát a VHDL-ben kell végrehajtani.

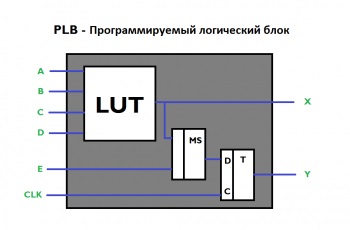

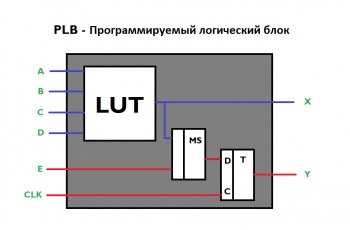

Vegye figyelembe az FPGA legkisebb részét, amelyet PLB-programozható logikai blokknak neveznek.

A PLB egy LUT-egyező asztalból, egy multiplexerből és egy D-flip-flopból áll. Kezdjük a LUT-val. Tény, hogy a LUT - statikus véletlen elérésű memória (RAM -. Random Access Memory egy felejtő memória, amely törlődnek a teljesítmény adatokat (beleértve Felvett Ki Be újra, és minden rögzített adatok törlésre kerülnek) nagy sebességgel ..... sebességgel.), amelyben az A, B, C, D értékek által létrehozott X kimeneti értékek tárolódnak.

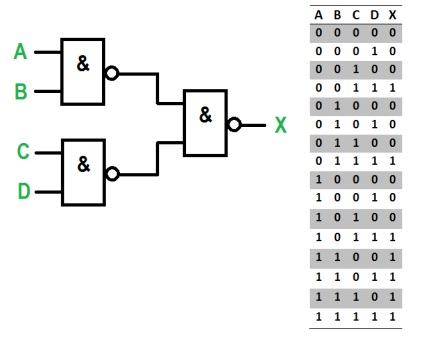

Tegyük fel, hogy az alábbi ábrán bemutatott FPGA áramkörre kell kiterjeszteni a megfelelő igazságtáblával:

Az A, B, C, D jeleket a LUT bemenetre táplálják, majd a LUT-ban tárolt igazságtáblából az X jel azonnal létrehozásra kerül, minden nagyon egyszerű. A kódban így néz ki:

X <= (A nand B) nand (C nand D);

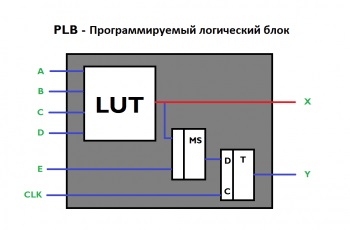

Az alábbi ábrán a piros vonal azt mutatja, hogy a kimeneti jel a hardver szintjén jön létre:

De mi lenne, ha szinkronizálni kell a jel órajel-frekvencia? Majd a konfiguráció az írás, meg kell határoznunk, hogy a kimeneti jel lesz telepítve vagy az első (rising_edge (CLK)) vagy a szelet (falling_edge (CLK)) Az órajel CLK és a fordító kerül a kimeneti jel c X kilépés, kiadási Y. a nyelv VHDL ez így néz ki:

ha (rising_edge (clk)) akkor

Y <= (A nand B) nand (C nand D);

A hardver szintjén ez a helyzet: a LUT jelzése megy a T flip-flopra, amely az Y kimenet értékét CLK-ra állítja.

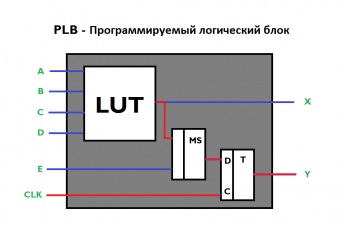

Mi van, ha késleltetni kell a bemeneti jelet egy órai ciklusban? Ezután a konfigurációban hozzárendeljük a szinkronizált CLK folyamat új jeléhez késleltetett jelet:

ha (rising_edge (clk)) akkor

Ez így történik az alábbi hardverekkel:

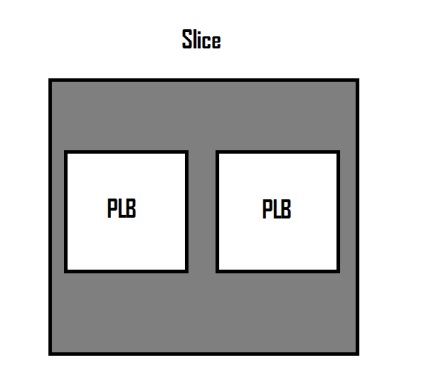

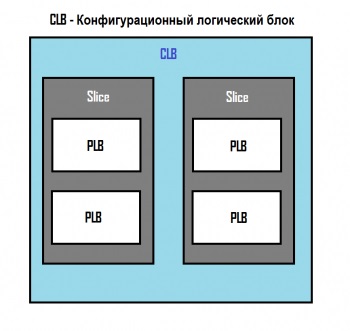

Emlékszem, hogy a fentiek mindegyike az FPGA egyik legrégebbi eleme, azaz a PLB keretében zajlik. De az FPGA-n belül több tízezer ilyen PLB (és talán több száz, a technológiák is: nem állnak meg), amelyek kapcsolódhatnak egymáshoz. A kapcsolatok megkönnyítése érdekében az FPGA egy moduláris elvet alkalmaz: a kicsi nagy: két PLB alkot egy SLICE-t.

Végezetül szeretném elmondani, hogy miért kellene az FPGA-t, és különösen az FPGA-chipeket megvizsgálni. Először is ez egy korlátlan mező a kreativitáshoz: szükség van egy egzotikus 13 bites időzítőre / számlálóra? - Vedd el. 15 UART szükséges? - Könnyű. Adatok küldése 6 Gbps sebességgel? - Nem kérdés. És ha az FPGA előnyei nyilvánvalóak, akkor lépjünk át arra, hogy melyik előnyös: CPLD vagy FPGA? Szeretném megjegyezni, hogy valójában minden az alkalmazástól függ. Ha a projekt nem nagy, de speciális perifériákat igényel, akkor ez CPLD. És ha rugalmasságra és nagyon nagy sebességre van szükséged, akkor ez FPGA. Semmi sem akadályozza meg, hogy ezt egy bizonyos ponton FPGA időben dolgozott először az egyik változata, de aztán a második, harmadik, ötödik, tizedik (konfigurálható tulajdonságai), mert ellentétben a többi chip, az erőforrás-felvétel / törlése az FPGA hajlamosak a végtelenig (amikor utoljára módosította a RAM a számítógép annak a ténynek köszönhető, hogy kifejlesztett egy erőforrás az írási / törlési? ez az, amit tudok. Tulajdonképpen ez minden, köszönöm a figyelmet

Itt vagyok a kapcsolódásodon, láttam a minimális alaplapot az ALTERA FPGA CycloneII készülékkel, amely az EP2C5T144-re épült. Tehát, miről beszélek, hogy használjam ezt a fórumot, csatlakoznom kell egy külső flash memória chiphez? Vagy a firmware lesz betöltve egy bytblaster minden egyes alkalommal, amikor a tábla be van kapcsolva, és ez működni fog, amíg a tápfeszültség ki van kapcsolva külső memória nélkül?

Maga a debug kártya már rendelkezik memóriakártyával, ahol a firmware tárolódik, így nem kell személyesen forrasztania a memóriát. Ami a vaku folyamat, amikor varrni, a környezet felajánlja, hogy válasszon, ahol letölthető firmware: az FPGA chip vagy flash chip. Ha betölti az FPGA, akkor igen, a készüléket kikapcsolja firmware törlődik, ha FLASH, akkor a készülék ki van kapcsolva során a firmware villog, akkor is, ha újraindítja FPGA maga fogja betölteni a firmware FLASH, segítsége nélkül ByteBlaster'a.

Ahhoz, hogy válaszolhasson, tudnia kell, mennyit vásárolnak meg.

Általában azonban a kezdőknek ajánlani kell a normál FPGA-t, nem pedig CPLD-t, és többé-kevésbé modern generációt, például

És a kezdetektől jobb, ha Alteráról van szó, megfelelőbb és vizuális szoftverrel rendelkeznek.