ModelSim szimulátor

ModelSim szimulátor

Szeretnék beszélni egy kicsit a digitális szimulációs projektek. Igen, igen. Ez a téma már többször felmerült, és természetesen - egy kimeríthetetlen téma. Még egyszer írt a szimulációs eszközök Quartus II változat 9. de a legújabb verzióját Quartus II v10 a „natív” alterovskogo szimulátor többé. Hogy megmondjam az igazat, én ideges. A kis projektek esetében ez szimulátor elég. Aztán írtam egy cikket a iverilog szimulátor - egy egyszerű, nyílt forráskódú szimulátor - elég tisztességes dolog. És most szeretnék röviden beszélni a program ModelSim:

Fogok beszélni egyik változata, azaz a ModelSim Altera Starter Edition.

Ott megjelenik egy táblázat összehasonlító jellemzőit különböző változatai ModelSim:

Úgy döntünk, Starter Edition - ez ingyenes, nem igényel engedélyt lehet használni a kis projektek akár 10.000 sornyi kódot. Azt hiszem, nem elég, hogy fejét. Átadjuk az alábbi letöltési linkre. Azt verzióját válasszák a Windows. fájlméret letöltendő - 586Mb. Ez nem kicsi, de nem túl sok jelenleg. Általánosságban, a rock és set ..

Most azt akarom, prosimulirovat ugyanazt a példát, amely már sikeresen próbáltuk utánozni a iverilog. Ez a két szamlalo.v fájlt és tcounter.v - azok helyét az én mappa C: \ Altera \ 10.0 \ projektek \ először.

A tartalom ezen fájlok itt:

szamlalo.v - egy számláló párhuzamos terhelés. Ha WR jel aktív ebben a pillanatban az első clk. regiszterben a számláló száma beviteli busz wdata rögzítésre. Ellenkező esetben a számláló értéke eggyel nő mindegyik első clk.

modul számláló (

bemeneti huzal visszaállítása,

bemeneti huzal clk,

bemeneti huzal [7: 0] wdata,

bemeneti huzal wr,

kimeneti reg [7: 0] adatok

);

Mindig @ (posedge clk vagy posedge visszaállítás)

if (reset)

adat <= 8'h00;

más

if (WR)

adat <= wdata;

más

adat <= data + 8'h01;

És ez - vcounter.v - „testbench” az én számláló. Ez a program használható, hogy ellenőrizze a helyes működését a számláló modult.

`Időskála 1ns / 100PS

modul test_counter;

reg visszaállítása, CLK, wr;

reg [7: 0] wdata;

drót [7: 0] data_cnt;

számláló counter_inst (reset, CLK, wdata, WR, data_cnt);

kezdeti

kezdődik

clk = 0;

reset = 0;

wdata = 8'h00;

WR = 1'b0;

# 50 reset = 1;

# 4 Reset = 0;

# 50;

@ (Posedge CLK)

# 0

kezdődik

wdata = 8'h55;

WR = 1'b1;

vég

@ (Posedge CLK)

# 0

kezdődik

wdata = 8'h00;

WR = 1'b0;

vég

vég

kezdeti

kezdődik

# 400 $ befejezni;

vég

kezdeti

kezdődik

$ DumpFile ( "out.vcd");

$ Dumpvars (0, test_counter);

$ Dumpvars (0, counter_inst);

vég

kezdeti

$ Monitor ($ stime alaphelyzetbe clk wdata wr data_cnt .....);

Itt vannak a fájlok megpróbálom bizonyítani használata ModelSim munkát.

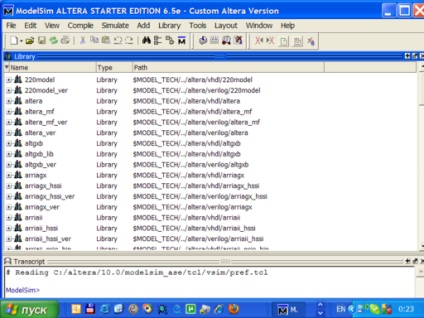

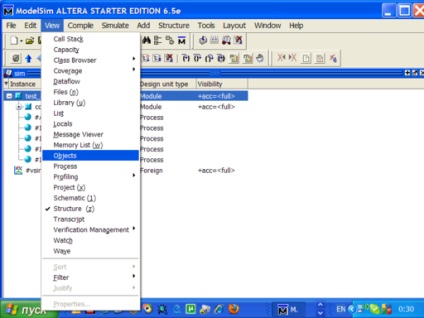

Amikor futtatja a programot ModelSim látunk ilyesmit képernyő (kattintson a képre a nagyobb):

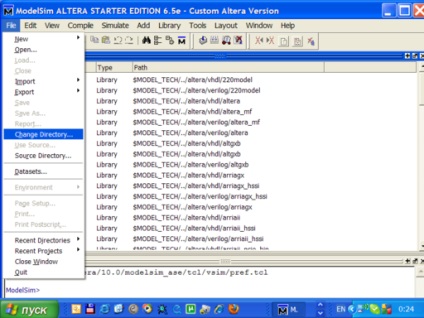

Az első dolog, amit tennie kell -, hogy menjen a munka mappát. Ehhez válassza ki az elemet a File / Change Directory menüben.

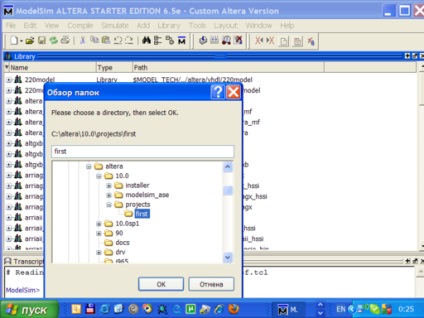

A párbeszédpanelen adja meg az utat, hogy a projekt:

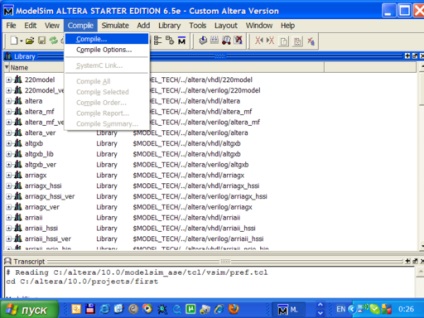

Miután kiválasztotta a mappát, akkor le kell fordítanunk a projekt a könyvtárban. A választás penkt Compile / Compile menü.

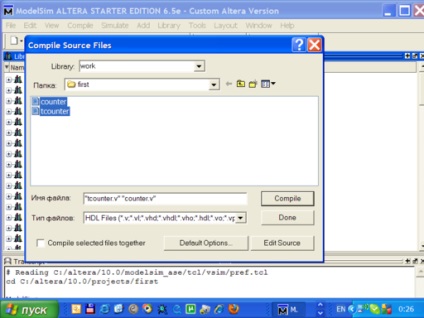

Itt ki kell választani az összes fájlt a projekthez. Dialog lehetővé teszi, hogy válassza ki egyszerre több fájlt.

Válasszon ki egy fájlt - kattints Compile gombra.

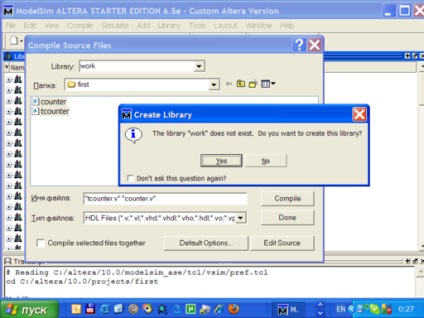

ModelSim kéri a könyvtár nevét kell létrehozni. Alapesetben a nevét a munkát. Nos ez legyen meg. A válasz igen. Miután összeállítása a Transcript ablakban ellenőrizze, hogy nincsenek hibák a forrás fájlokat.

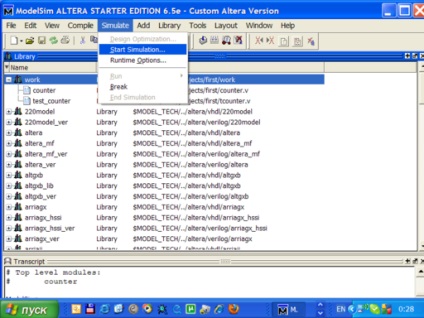

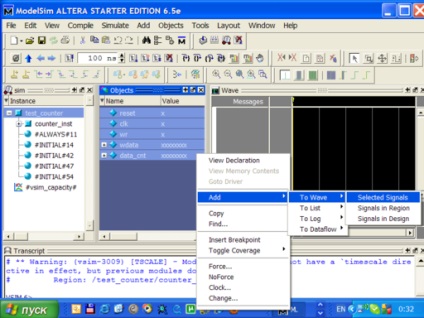

Megjegyezzük, hogy a könyvtár ablakban egy új könyvtári munkában. mint amilyennek lennie kellene. Most válassza ki az elemet szimulálása / Start Simulation menü.

Tehát most lássuk, mit teszünk a szimulációban. Azt, hogy néhány lépést előre szimuláció kiválasztásával szimulálása \ Run \ Run100.

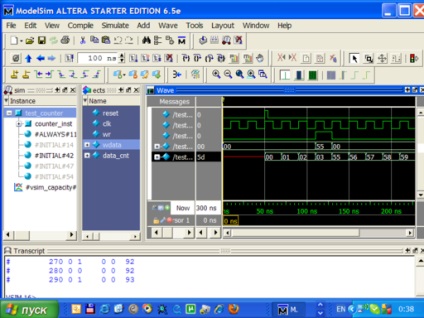

És itt van a szimuláció eredménye:

Megjegyezzük, hogy szöveges kimenetet a Transcript ablakban, és a jelek magukat a Wave ablakban ugyanazok, mint abban az esetben a szimuláció segítségével nyílt forráskódú Icarus-Verilog.

Nos, itt - a jelek formájában láthatjuk, hogy a számláló megfelelően működik - így tervezett nálunk!

Valaki segítsen telepíteni ModelSim a ubuntu.Pri indítási problémák „./vish: betöltése közben hibát megosztott könyvtárakat: libXft.so.2: nem lehet megnyitni megosztott objektum fájlt: Nincs ilyen fájl vagy könyvtár”.

megpróbálja telepíteni további könyvtárak sudo apt-get install libxft2

Valaki segítsen telepíteni ModelSim a ubuntu.Pri indítási problémák „./vish: betöltése közben hibát megosztott könyvtárakat: libXft.so.2: nem lehet megnyitni megosztott objektum fájlt: Nincs ilyen fájl vagy könyvtár”.

Moline idézve Dmitry:

Ugyanez a probléma, mint Vadim és Ia.

Összes termel egyenes vonalak, bár mindent megtett, mint írva a cikkben. Csak írtam programot, és még megpróbált nézd meg a munkáját elemei a standard könyvtár, de az eredmény ugyanaz.

Ugyanez volt a helyzet, úgy döntött, a következő: ha a Szimulációs \ Start Simulation választani csak egy testbencha fájlt, úgy döntöttem, az első két - egyenesek. Hogy az impulzusok hasonlóak voltak a screenshotok, akkor kicsinyíteni a chart (jobb klikk - talál alább).

Megvan - ha megadjuk mindkét modul (tesztelés és a testbench) egyetlen fájl ModelSim nem lesz képes megjeleníteni szimulációs eredmények alapján. Nos, mindez lehetséges?

Használja huzal típusú szimuláció a kimeneti jel, nem csak a reg akkor nem „bolt” jel állapota a nyilvántartásba, és hogy elkerüljék a hardver költségek?

Uram, soha nem tudni, hogy ki fog reagálni, ha elolvassa a cikket megjelent egy pár hülye kérdéseket:

1) Lehet-e levelet testbench ugyanabban a fájlban a teszt modult, egy testbench van megvalósítva egy egységet? (Tudom, pökhendi, mert könnyű a Google, de vajon kinek kevés, nem teher)

2) Miért hozzon létre egy (bejelentett) jelvezeték [7: 0] data_cnt a testbenche?

Értem helyesen:

számláló counter_inst (újra beállítva, CLK, wdata, WR, data_cnt); - ezt a sort hozunk létre egy példányt a modul számláló és helyettesíti a kimeneti regiszter adatok jel data_cnt? és mi az értelme ennek a cselekvés, hogy miért nem lehetett cserélni a jelet a neve megegyezik egy adat, vagy akár adat regiszter, mind a teszt modult? Általában kimeneti regiszter testbencha vagy mindig szükséges, csak a jel, mint a kimeneti?

Ugyanez a probléma, mint Vadim és Ia.

Összes termel egyenes vonalak, bár mindent megtett, mint írva a cikkben. Csak írtam programot, és még megpróbált nézd meg a munkáját elemei a standard könyvtár, de az eredmény ugyanaz.

Ugyanez volt a helyzet, úgy döntött, a következő: ha a Szimulációs \ Start Simulation választani csak egy testbencha fájlt, úgy döntöttem, az első két - egyenesek. Hogy az impulzusok hasonlóak voltak a screenshotok, akkor kicsinyíteni a chart (jobb klikk - talál alább).