Típusú programozható logikai

Ez függ a technológia

Tehát az első dolog az első.

Abban az esetben a biztosítékot vagy PROM programozó vagy „égnek”, hogy megszüntesse megolvasztjuk az olvadó híd jelenlegi impulzus időtartam, nagy amplitúdójú. Ezért, biztosíték-eszköz nevezzük egyetlen programozható. Rövidzárak fém (nikróm, titán-volfrám) vagy polikristályos (poliszilícium).

Abban az esetben, elektromosan programozható EPROM áramkör egy speciális programozási és törlik besugárzással felszíni kristály erős ultraibolya fényt (például egy higanylámpával) keresztül kvarcüveggel a házban.

SRAM vagy orosz statikus RAM véletlen elérésű jellemző az alacsony fogyasztás, ezért úgy véli, annak alkalmazása az FPGA. Ez a fajta memória cella áll 6-8 tranzisztorok, ezért az alacsony sűrűségű felvételt és a magas költségek kilobyte információ tárolására. Általában, minden egyszerű és hétköznapi.

De antifuse - a legérdekesebb. Hogy ők építették a nagyon kemény Rad-FPGA (RTAX és RTSX-SU) cég Actel, amely által olyan híres. Mint abban az esetben a biztosíték, hogy egyszer olvadó (bár nem mindig, de erről bővebben később). Azonban a tervezés egy alapvető különbség - alkottak háromrétegű dielektromos az oxid-nitrid-oxid (ONO), és az ellenkezője.

Kezdetben az interneten van egy ilyen nagy ellenállás, elérve több millió ohm. Amint a feszültség között alkalmazzuk a diffúziós réteg és a szilícium-gumiabroncs (az ábrán - kapu) megjelenéséhez vezet a oxidot alagút hatás Fowler-Nordheim alagút hatás és a közvetlen. Ez növekedéséhez vezet a szivárgási áram és a lágy bontás (bontás reverzibilis). Ha az elektromos tér megszűnik, a dielektromos ellenállást helyreállítani. Ellenkező esetben áramok növekedni fog, és ez végül a termikus (irreverzibilis) a dielektromos letörés, a kialakulása egy vezetőképes csatorna, és egy éles növekedése a rajta átfolyó áram. Ez a szkript a nyugati irodalomban nehéz bontásban.

jumper állapotjelei a szünet után is fenn kell tartani kb 40 éve. Alacsony ellenállás és az alacsony parazita találóan sti antifuse típusú kapcsolatok pozitív hatással van a sebesség-prevalenciája neniya jelek programozható kapcsolatokat.

Under maszk programozási alkalmazást jelent, a kristály-1-2 félkész felső fémrétegben majd maratással.

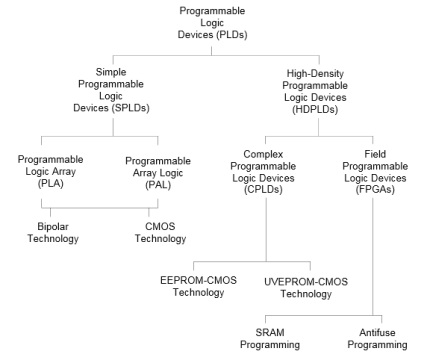

Térjünk át hosszas bevezetés, sőt, hogy a téma a címben jelzett. PLD készülékek számától függően a kapuk, az architektúra és funkciók a programozási technológia rendelt osztályok képviselt program az alábbi

Gate array (FPGA)

A terminológia elfogadott a nyugati vagy más néven HAL (Hard Array Logic) vagy strukturált ASIC. Valami közötti specifikus integrált áramkör és a PLD. Az első az a közös, hogy a programozás történik technológiailag. A második az, hogy egyetlen chip kaphat a különböző digitális eszközök.

Programozás alkalmazásával végezzük el 1-2 majd maratással a fémezés rétegek a kristály félkész a neskommutirovannymi sejtek. Épült FPGA hardver fejlesztők lehetősége van a cseréje LSI alapú FPGA, míg a fogadó, néhány esetben jelentős gazdasági hatása és a növekvő elrendezés sűrűség berendezés. Annak érdekében, hogy az ilyen feldolgozás gyártók fejlődő CAD szoftver lehetővé teszi az automatikus fordítás végrehajtott projektek alapján FPGA FPGA könyvtárak.

Állhat akár 100.000 kapuk és működtetni frekvencián az 50MHz. A működési ciklus körülbelül 3 hónap.

Jelenleg szinte teljesen kiszorította a FPGA és CPLD. Azonban alkalmazni kisüzemi termelés tekintettel annak honnan kapcsolatban bejegyzett chipek. Elérhető a hazai az Á. Civil szervezetek a fizika és más vállalkozások számára.

Programozható Array Logic (PAL)

Ez áll az input-output logikát és a mag, amely egy jól ismert mindannyiunk EPROM vagy EEPROM. Létrehozásához használt kobinatsionnyh logichekih áramkörök. Mert prorgammrovaniya PAL suschestovali speciális programozási nyelvek, mint PALASM, BAL, CUPL. Korai PAL által termelt bipoláris technológia egységes programozási keresztül kiégés titán-volfrám bordák (biztosítékok). Később - a CMOS technológia. Ezek közé tartozik a tíz több száz szelepek.

BMC mára már túlhaladott kifinomultabb eszközöket, de még ma is használják termékek speciális célokra, mint például a katonai felszerelések. Gyártó Atmel

Programozható logikai tömb (PLA)

Ez eltér a korábbi osztály vannak programozva egy tömbben VAGY és ÉS. Emiatt - és bonyolultabb rendszerek költsége magasabb, mint a PAL. Annak a ténynek köszönhetően, hogy mindkét tömb programozható, a sebesség kisebb, mint abban az esetben, PAL.

Komplex programozható logikai eszközzel (CPLD)

Technológiai programozható logikai eszközök, a komplexitás, amely elfoglalja a körülbelül PAL (Programozható Array Logic) és FPGA (Field-programmable gate array), és egy kombinációja az építészeti jellemzői.

Eszköz CPLD is több ezer - több tízezer sejtek jól kiszámítható terjedési késleltetés. Tól FPGA megkülönböztetni a jelenléte nem felejtő újraprogramozható memóriában, azokat a kezdeti terhelés a konfiguráció nem igényel memória chip, mint abban az esetben az FPGA. Ezért átprogramozása erőforrás kisebb, mint abban az esetben az utóbbi (nem kevesebb, mint 1 000 ciklus / felvétel törlése a Xilinx CoolRunner-II család).

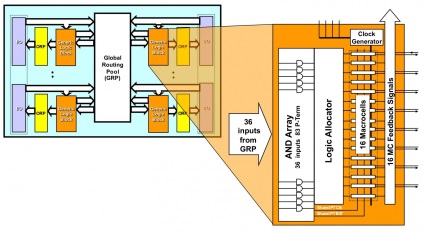

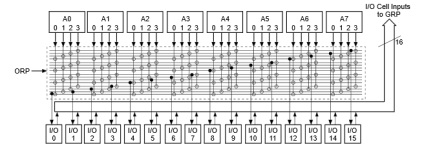

CPLD szerkezet egy sor funkcionális blokkok egyesült mátrix kapcsoló Global Routing Pool. Az architektúra funkcionális blokk (Generic Array Logic) sok szempontból hasonlít az építészet egyetemes PAL. A különbség abban rejlik, hogy az összes kimenő makrocella (makrocellákat) két visszacsatolások, és a köztes busz makrocellákat vannak rendelve keresztül forgalmazó (Logic lefoglaló). Néhány makrocella CPLD nincs összefüggésben a külső kimenet. Ilyen makrocella úgynevezett rejtett. Rejtett makrocella csak egy visszajelzést.

Külső kimenet CPLD kötődnek kiadási makrocella egy másik mátrix mezhsodineny ORP (Output Routing Pool). Ugyanez mátrix köti össze a bemeneti logika a GRP. Hogy csökkentsék a késések egyes CPLD közvetlen bemenetet bemenetek közvetlenül kapcsolódik a bemenetek makrocellákat.

Field-Programmable Gate Array (FPGA)

Annak ellenére, hogy a különbség a különböző FPGA családok és a különböző gyártók, amelyek szerepelnek azok összetétele finomságok, mint a DSP és a processzor mag egységek általános elveinek FPGA architektúra változatlan marad.

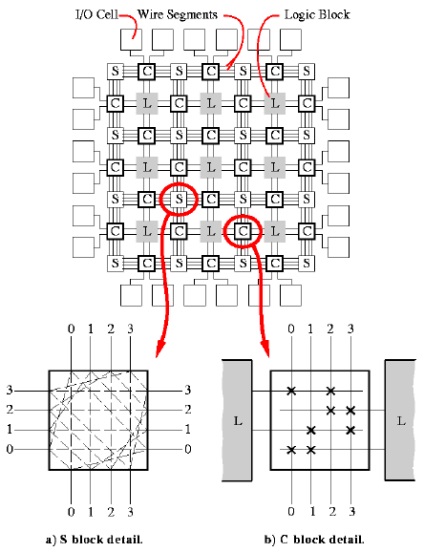

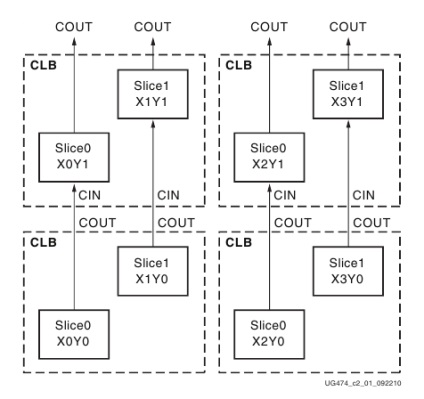

A fő funkcionális egysége FPGA CLB (konfigurálható logikai blokk). CLB kapcsolás által végzett S (csatlakozódoboz) blokk és a C blokkok. CLB, viszont magában foglalja a többszörös LUT (Look-up table). A cég Xilinx CLB is állhat egy úgynevezett szeletek, ami szintén, viszont áll Ľutov. Akkor miért bonyolítaná a dolgokat? Az a tény, hogy vannak különböző típusú szakaszok Szelet, luty amelyek különböző funkciókat.

Az FPGA családok Virtex-6 és a Spartan-6 CLB áll 2 rész 3 fajta: SLICEM, SLICEL és SLICEX. A családi Spartan-6 egy CLB tartalmaz SLICEL és SCLCEX, és a többi a SLICEL és SLICEM. A Virtex-6, úgy néz ki, egy kicsit más - az egyik a 2 SLICEL rész, és a második - és SLICEL SLICEM. Az egyes szakaszok egy CLB csatlakozik egy külön láncátvivő.

Nézzük meg minden szekcióban.

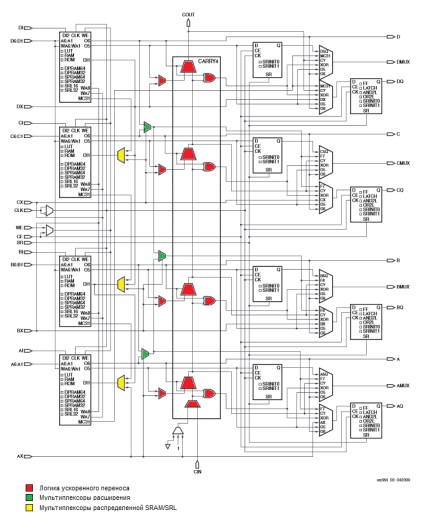

SLICEM tartalmaz 4 LUT, magában foglalja a logikája gyorsított szállítás, a konverziós táblázatot, amely lehet beállítani, mint egy elosztott memória és SRL (léptetőregiszter keresési táblázat), és a multiplexerek számának növelését Boole érvek

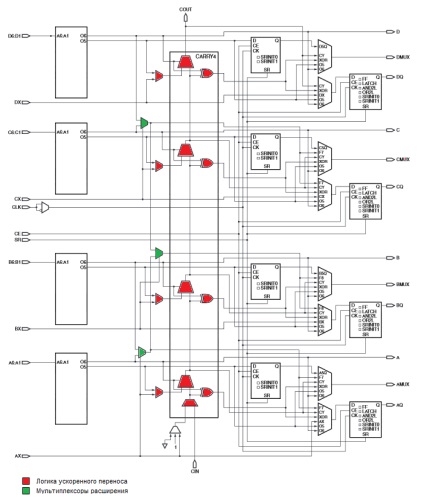

SLICEL tartalmaz 4 LUT tartalmazza logikai gyorsított szállítási és multiplexerek számának növelését logikai érvek

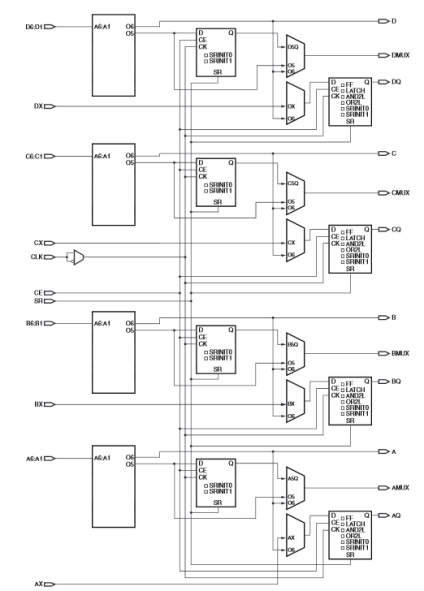

SLICEX áll 4 LUT, csak logika. Nem osztott memória, az átviteli áramkörök és multiplexerek bővítése.

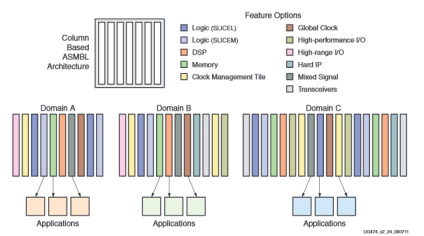

Mindez miként kapcsolódnak egymáshoz? Ebből a célból, a cég kifejlesztett egy Xilinx ASMBL építészet (Application Specific Modular Panel Architecture). Röviden, azonos blokkokat, például egy DSP, memóriablokk beágyazott IP-blokkok vagy logikai szakaszok vannak elrendezve egy sorban. Ezek egyesítésével sorozat és kapott FPGA szakosodott a különböző alkalmazások (például, Virtex-6 jelentése LXT, SXT és HXT).

IO egységek modern FPGA megmarad több mint 40 különböző protokollok különböző feszültségen, mint például: LVCMOS, LVDS, Busz LVDS, LVPECL, SSTL, HSTL, RSDS_25 (point-to-point), PCI, I2C és mások. Következtetések FPGA együtt a bankok 30-80 terminálok minden egyes bank terminálok támogatják a különböző szabványok csoportok.

- Soloviev, A. Klimovich, Bevezetés a design kombinációs áramkörök FPGA.

- Daniel Gomez-Prado, Maciej Ciselsky, A bemutató FPGA útvonal.