Hiba processzorok AMD Phenom x4

Köszönjük a támogatást!

Tesztágy konfigurációk

Állvány №1 (nincs „foltok”)

Állvány №2 (a "patch")

Valódi sávszélesség adat-gyorsítótár / Memória

Először is megjegyezzük, hogy ebben a tanulmányban felsorolt abszolút tesztek AMD Phenom X4 platform „patch” némileg eltérnek a korábban beszerzett (anélkül, hogy „tapasz”) használata miatt különböző alaplap (lásd. Tesztágy konfiguráció). Különösen abban az időben a tanulmány az első rendszer (stand №1, alaplap MSI K9A2 Platinum) nem volt ismeretes, hogy milyen frekvenciájú északi híd és az L3-cache a processzor az alapértelmezett beállítás a rendszer. Figyelembevételével ebben a cikkben, hogy a második rendszer (stand №2, alaplap Gigabyte MA790GX-DQ6) AMD Overdrive segédprogram mutatta gyakorisága a memória vezérlő és L3-cache alapértelmezett processzor beállítása 2,0 GHz-es frekvenciájú 2,4 GHz-es processzormag. Ésszerű azt feltételezni, hogy az azonos bánásmód „default” használják az első a vizsgált alaplapokkal. A jelen tanulmányban azt megnövekedett gyakorisága Northbridge processzor 2,4 GHz-es kezűleg BIOS konfiguráció szinkronicitás működését processzormagok és az integrált memória vezérlő, és összehasonlítjuk az üzemmódban a processzor egy „default” üzemmódban (CPU 2,4 GHz-es, NB 2,0 GHz).

Eredmények sávszélesség mérése (MS) adatfeldolgozó gyorsítótárak és a memória táblázatban mutatjuk be. 1.

Átlagos valós sávszélességet, bájt / ciklus

5,23 GB / s (40,9%)

3,43 GB / s (26,8%)

* Zárójelben az értékek a elméleti határ PS memória busz

Amint az várható, a sebesség jellemzőit L1 és L2-gyorsítja az adatfeldolgozó magot használ „patch” nem változik. Velocity jellemzőit L3-cache több második rendszerben a növekvő (8-11%), míg a nagy sebességű memória alrendszer jellemzői határozottan csökkent (különösen az olvasás CAP, mintegy 18%). Már ebből a vizsgálati eredmények is, hogy az előzetes következtetésre jutott, hogy a kérelmet a „patch” nincs jelentős hatása a L3-cache processzor (annak PS következtében növekszik a megnövekedett annak mértéke 2,0-2,4 GHz, míg az SS erősítés kisebb képest 20% -os növekedést), de hatással van a KAP (növekedése ellenére az órajel a memória vezérlő). állítás a hiánya a befolyása „foltok” a jellemzői a L3-cache megerősítette további vizsgálatok.

Legnagyobb Valós Memória Sávszélesség

Korlátozó tényező a valós memória sávszélesség táblázatban. 2, abban az esetben a „foltok” a következők: maximális valós memória olvasási sávszélessége csökken 19,5%, a belépés - mintegy 4,5%.

18,2 ns

18,6 ns

39,0 ns

225,8 ns

* Panel mérete 32 MB

Kvantitatív tulajdonságokkal látencia L1-, L2-, és L3-cache, táblázatban mutatjuk be. 3 bizonyítani gyakorlatilag teljes változatlanság az alkalmazás „foltok”, ami ismét megerősíti, hogy nem a befolyása a „foltok” a L3-cache processzor. A memória várakozási megnövekedett mennyiségben (körülbelül 13% a pszeudo-véletlen hozzáférésű, és több mint 2,6-szer (!) Egy véletlen hozzáférés) mutatnak jelentős romlása a sebesség jellemzőit az utóbbi egy csúszás állapota L2 D-TLB processzormagot (azaz, a ha ezek a hibák kell „maszkolt” nem dokumentált szerkezete «TLB» processzor memória vezérlő le van tiltva a alkalmazásának „tapaszok”).

Minimális várakozási idő cache adatmemória és

A vonatkozó következtetéseket az átlagos várakozási idő az adatok cache és memória értékek teljesen kitolható az esetben a minimális késleltetést táblázatban megadott. 4. Jellemző megjegyezte csökkenése hatékonyságának hardver előzetes letöltési megnyilvánuló növekvő memória késleltetés előre és hátra a bejárást alkalmazás „foltok”, bár ez nem tekinthető közvetlen következménye letiltása «TLB» processzor memória vezérlő.

A szint hozzáférési mód

Minimális várakozási idő ciklus (ns)

* Panel mérete 32 MB

** A zárójelben megadott értékek kapott №2

Az asszociatív adatok cache

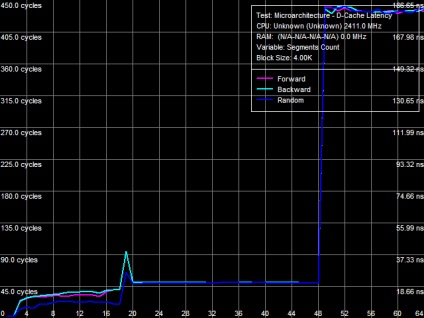

Az eredmény a mérési asszociatív L1-, L2-, és L3-gyorsítótár adatok (ábra. 2) nincs különbség szempontjából értékek maguk asszociatív cache, azonban jelentősen különbözik finom „slip asszociatív” minden cache szinten, ami megfigyelhető, ha a több mint 48 gyorsítótár szegmenseket. Ez a hatás nyilvánvalóan rokon hatása Slip L2 D-TLB, amikor látencia memória-hozzáférések kell maszkolni TLB memória vezérlő.

Ábra. 2. Az asszociatív az adatok cache

Az aktuális adatátviteli sebesség L1-L2 gyorsítótár Bus

Mivel az átlagos valós PS L2-gyorsítótár, az igazi alállomás busz L1-L2 (lásd. Táblázat. 5), szintén érik változások, amikor a „patch”.

Valós L1-L2 sávszélesség, byte / ciklus

Phenom X4 nélkül "patch"

Phenom X4 egy "patch"

Olvasás (előre)

Reading (hátra)

Entry (közvetlen)

Felvétel (reverz)

Az aktuális adatátviteli sebesség busz L2-L3 cache

Ami a tényleges PS L2 busz (CPU mag) -L3 (memória vezérlő), a teljesítmény jellemzőit (lásd. Táblázat. 6), mint a korábban mért PS L3-cache, ezen a rendszeren valamivel magasabb (körülbelül 8%) a miatt a nagyobb sebességet a processzor memória vezérlő (2,4 vs. 2,0 GHz).

Az aktuális adatátviteli sebesség L2-L3, bájt / ciklus

Phenom X4 nélkül "patch"

Phenom X4 egy "patch"

Olvasás (előre)

Reading (hátra)

Entry (közvetlen)

Felvétel (reverz)

utasítás cache, a valós sávszélességet dekódolás / végrehajtását a kódot

Nyilvánvalóan nincs hatása „patch”, és a dekódolási sebesség / végrehajtási utasításokat L1-I, valamint az L2-cache processzor mag (lásd. Táblázat. 7). Ugyanakkor, a gyorsaság a kódot L3-cache ismét növekszik (körülbelül 8% megegyezik az SS L3-cache) a megnövekedett gyakorisága az utóbbi 2,0 a 2,4 GHz-es.

használati típus

(Méret, byte)

A tényleges dekódolás / végrehajtási sávszélesség bájt / ciklus (utasítás / ciklus)

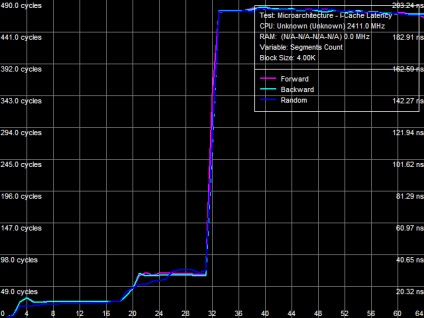

cache asszociativitás

Test asszociatív utasítás cache (3.) Azt mutatja, egy meglehetősen érdekes képet. Nevezetesen, az ő eltűnő, amelyet az előző vizsgálati sorozatban (anélkül, hogy a „patch”) a második inflexiós asszociativitása L3-cache a területen körülbelül 50 cache szegmensek. Ugyanakkor, mivel a vizsgálati asszociatív adatok cache, jelentősen növeli a bírság „slip asszociatív” utolsó szintű cache processzor. Ezért arra lehet következtetni, hogy a hatékony L3-cache asszociatív cache-a kód 14 (32 mínusz 18), a korábban megfigyelt, a második kanyarban 50 szegmensek egy tárgy.

Ábra. 3. Az asszociatív adatok cache

Jellemzők TLB

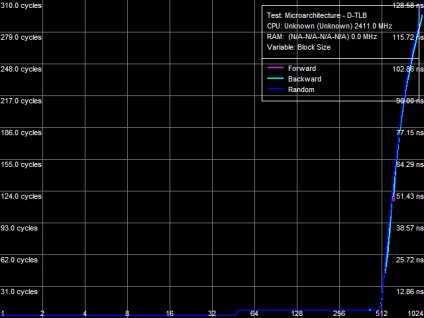

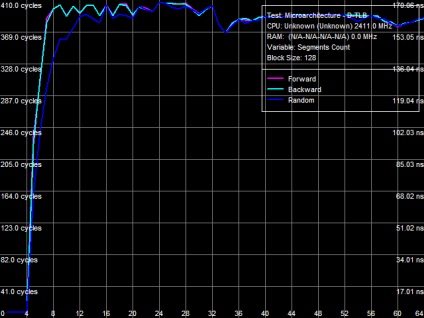

Amint az várható volt, a legnagyobb hatást a felvétele „foltok” show TLB processzor tesztek. Természetesen a nagyon jellemzőit TLB nem változik (mivel ezek az elemek tartoznak a processzor mag), de jelentősen növeli a büntetés miss utolsó szinten TLB a „méret” és „asszociatív”.

Ábra. 4. A mennyiségű D-TLB

Ábra. 5. asszociativitás L2 D-TLB

Ábra. A 4. ábra a méret a teszt eredménye a D-TLB, és ábra. 5 - a vizsgálati asszociatív L2 D-TLB. Mindkét esetben van egy jelentős növekedés a finom csúszás L2 D-TLB - körülbelül 290 ciklusokat a kimerültség térfogatának akár 400 ciklus kimerítette asszociatív.

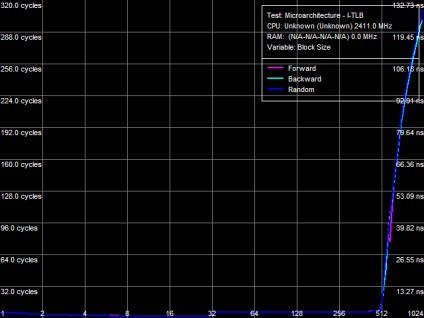

Ábra. 6. Size I-TLB

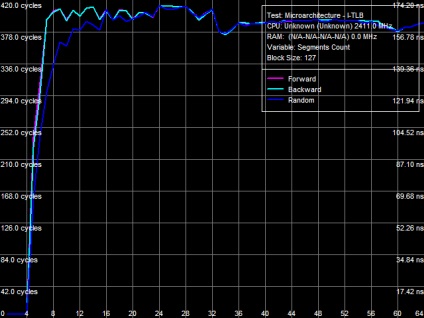

Ábra. 7. asszociativitás L2-I-TLB

Hasonló eredmény Vizsgálatok azt mutatják, mérete (ábra. 6) és asszociativitás (ábra. 7) I-TLB. PIM slip L2-I-TLB «méretű» összeg körülbelül 300 ciklus, és a „asszociatív” - körülbelül 400 ciklus, amely közel van a megfelelő értékeket kapott tesztek D-TLB.

Milyen következtetések vonhatók le a kutatás eredményei? Először is, nyilvánvaló és fontos következtetés, hogy a feldolgozók AMD Phenom család (K10), valamint az AMD Athlon 64 (K8) nem tartalmaznak az integrált memória vezérlő, egy szerkezet, amely lehet tekinteni a puffer TLB elég nagy egyaránt hatásos kezelése során adat (D-TLB), és a teljesítménye a kód (I-TLB). Léte a szerkezet mindkét család processzorok bizonyult mérsékelt csúszás értékeket rendelni finom utolsó szinten (L2) D-TLB és az I-TLB processzormag található 20-40 ciklus. Ugyanakkor, tiltsa le (és ez - a legésszerűbb magyarázat arra, hogy a „patch” AMD Phenom processzorok) vezet jelentős növekedése a mennyiség tekinthető finom csúszás (akár 300-400 ciklus, azaz majdnem egy nagyságrenddel!) . Ebben az összefüggésben az is érdekes megemlíteni a „energiatakarékos” AMD Athlon 64 X2 EE. amelyben a finom csúszás L2 D-TLB és az I-TLB kezdetben magas. Abból lehet kiindulni, hogy ezek a processzorok szerkezet „a TLB” memória vezérlő található, vagy egyáltalán nem (ami nem valószínű, mivel lehetetlen azt mondani, hogy ez így nehéz végrehajtani, és fogyaszt annyi energiát, hogy volt elég zárni a „energiatakarékos” változat a processzor), vagy ... off kezdetben jelenléte miatt a hiba, hasonló egy hiba a Phenom processzor memória vezérlő (sokkal nagyobb valószínűséggel).

Az alábbi következtetést lehet levonni a vizsgálati eredmények abban a tényben rejlik, hogy a szerkezet «TLB» említettük kifejezetten utal a vezérlő CPU memória és nem L3-cache (ahogy meg van írva a korai hibaüzenetet Phenom processzorok). Ezt támasztja alá a szinte teljes hiánya negatív befolyása a „foltok”, hogy a nagy sebességű jellemzők (PS és a késleltetés) processzor L3-cache. Így csökkenti a teljes rendszer teljesítményét, ha a „patch” miatt kizárólag a sebesség csökkentéséhez jellemzőit memória alrendszer és különösen jelentős növekedést látencia véletlen hozzáférésű memória. Az egyszerűség kedvéért képviselje őket az összesítő táblázatban.

Érték nélkül „patch”

Az értéket a „patch”

Az ötlet okozhat némi átlagolt hatás nagyságának a „foltok” egy ilyen töredékes alacsony szintű jellemzői meglehetősen értelmetlen - terjedt közötti értékeket 1,7% -ról 11,8-szer, és maguk hatások (például növelése bírság csúszik TLB) nem viselkednek jelentős módon a valós alkalmazások miatt exkluzív „szintetikus” jellemzők magukat. Ugyanakkor, egy közös csoportot lehet megkülönböztetni csökkenti a sebességet jellemzőit memória alrendszer (18-20%), kellően közel a valósághoz, ami hasonló a csökkenés a rendszer teljesítményét a legtöbb valós alkalmazások működnek adatok helyett „in-line” helyett „random „módon. Amikor a véletlen az adatokhoz való hozzáférést is várhatóan tovább csökkenti a teljes rendszer teljesítményét, mert a memória hozzáférés késleltetést ebben az üzemmódban igen jelentősen emelkedik.

Dmitry Bessedin