programozható processzorok

Hogy javítsa a bit CPU tevődik össze több szakaszból áll.

Annak ellenére, hogy jelenleg a kérdés megosztjuk feldolgozók megszűnik megfontolásra lehetővé teszi a mélyebb megértését elveinek építése és üzemeltetése modern single-chip mikroprocesszorok és rendszerek alapján rájuk. Ezt követően tekinthető particionált mikroprocesszor K584.

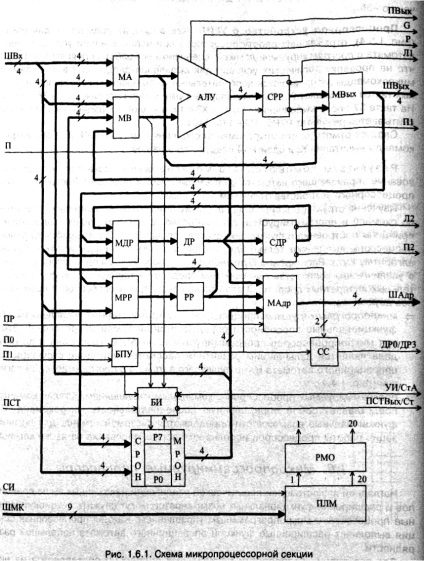

Strukturális és funkcionális szervezeti a processzor. A blokkvázlat szemlélteti egy külön mikroprocesszoros szakaszt ábra. 1.6.1.

A következő komponenseket tartalmazza a készítményben a szakasz:

● aritmetikai logikai egység (ALU). nyolc eszközt az aritmetikai és logikai műveletek nyolc. Az ALU kap bemenetek operandusok A, B és n ALU jelátvitel. Tól ALU kimenetek venni műveletek operandusok A, B, és ALU kimeneti PVyh transzfer és jelek G, R gyors transzfer;

● üzemi nyilvántartás (RR). ellátja az alapvető funkcióit információfeldolgozás;

● további (HLR). bővítése vagy dolgozó nyilvántartásban használt dupla pontosságú műveletek

● egység általános célú regiszterek (POH). amely nyolc regiszterek P0. P7 tárolására szolgáló és információcsere a lamellák között a blokkok. P7 regiszter általánosan használt feladatokat lát el a számláló, amely egy sorozat utasítás végrehajtása: a tartalom növekedésével a számláló végre egy következő mikroutasítás; növelve a két következő mikroutasítás hagyja; hiánya számláló üzemmódban használjuk belépő új tartalom P7, amely szükséges az átmenet végrehajtásának;

● helyzeti vezérlőegység (PCU). a szükséges változtatásokat a műveletben részén függően betöltött általa (primer, középső, bodza) processzor alkotja több szakaszból áll. A kívánt szekcióban megadott pozíció jelek útján P1, P0;

● váltókar és a kiegészítő üzemi regiszter (CRR, CRA) alkalmazásával BPA jelek lehetővé teszik, hogy a művelet végrehajtásához tartalmát az említett shift regisztert;

● választó áramkör (SS) kiválasztja a járulékos bitek HLR függően által elfoglalt szakasz. A kimeneti vonal eltávolítjuk difunkciós Jr. (DRO) vagy idősebb (DRZ) DR színtű tartalmát;

●-növelő blokk (BI) változtatására program számláló tartalmát a számláló függően a számláló bemeneti átviteli jel értékeket (FCS) és-növelő kontroll (M) érkezett a bemenet. A kimeneti blokk BI eltávolított-növelő számláló carry jelkimenet (PSTVyh) és a magasabb számjegye operandusok A (CTA) és a B (CTB). Üzemmódok kiválasztása CC áramkör és a blokk BI-növelő összehangolt jelek P1, P0 fogadná a bemeneti helyzetbe vezérlőegység BPU (táblázat. 1.6.1). A jeleket BI beviteli mód regiszter P7 - számláló vagy POH (táblázat 1.6.2.);

● a multiplexer (MA) vezérli a áthaladását az operandus egy a bemeneti busz vagy POH (ShVh), vagy a bemeneti a ALU kimeneti busz (ShVyh). A bemeneti és kimeneti busz áll 4 sor;

● A multiplexer (MB) vezérli az átmenetet az operandusok RR, DR, vagy ShVh input a ALU; egy kimeneti multiplexer (MVyh) továbbítja operandus A és operandus kimenetét az ALU a ShVyh vagy PP bemenetek, DR, POH;

● programozható logikai tömb (PLA) átalakítja a 9-bites mikroutasítás kód, amely belép a részben a mikroutasítás busz (MCS), tagjai 9-line, 20-bites belső ellenőrző szót, amely az irányítást az összes egység a mikroprocesszor szakasz;

● Regisztráció microoperations (RMS) tagjai 20 és D -triggerov, tárolására belső ellenőrző szót a mikroutasítás végrehajtási időt. Mikro regisztrációhoz RMO loading ami keletkezik az órajel pozitív él (a jel változik 0-1), lehetővé teszi, hogy a jelenlegi mikroutasítás termelni PLA veszi és konvertálja a következő mikroutasítás kódot.

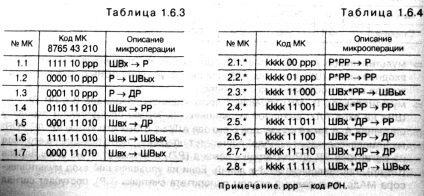

mikroutasítások rendszer. mikro-kód, amely kilenc számjegy (K8 ÷ R0). Használt két formátum a mikroutasítás kód:

● az első formátum egy sebészeti területen 4 MSB ÷ K5 K8, határozza elsősorban a ALU funkció; További mező bitek K4 és rövid. bővülő kódolási képesség; mezőválasztó a három legkevésbé szignifikáns bit K2 ÷ R0 (ppp), amely lehetővé teszi, hogy válasszon ki egy nyolc az POH, amely részt vesz az elvégzett mikro-ops;

● egy második formátum áll egy mező, amely az összes bit K8 ÷ R0 MC kódot.

A könnyebb mikroutasítások rendszer van osztva hat csoportban. Tekintsük a vonásait MV-csoport.

Csoport 1. Ezzel a MC-csoport (táblázat. 1.6.3) teljesülnek MO közötti átadás belső csomópontok IPU nélkül ALU. A információforrás a POH (P), vagy ShVh, vevő - POH (P) RR, DR, vagy ShVyh.

2. csoport Ebben a csoportban (táblázat. 1.6.4) tartalmaz aritmetikai és logikai műveletek által végzett ALU. A műveleteket az V. táblázatban közöljük. 1.6.4 A csillaggal (*) függ kkkk kódot és táblázatban felsorolt. 1.6.5. Ezeket a műveleteket az általános esetben a operandusok A és B, illetve keresztül érkező ALU multiplexerek A, B (ábra. 1.6.1) a források „Leírás UOP” oszlopban feltüntetett táblázat. 1.6.4 (bal oldali oszlop utal az operandus egy, és a jobb -, hogy az operandus B).

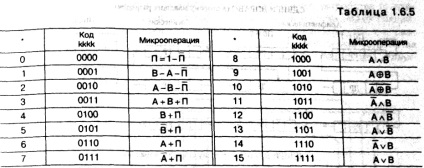

háromféle művelet kell (Táblázat. 1.6.5).

Műveletek két operandus. Ezek közé tartozik a három (1-3) számtani és mind a nyolc (8-15) logikai műveleteket.

Műveletek egyetlen operandus. Ezek a műveletek (4-7) lehetővé teszik az ALU elvégzésére átviteli közvetlen, inverz vagy kiegészítő kód operandusok A és B, valamint a szállítás lépésekben: A + 1, B + 1.

Kezelés nélkül operandusok. Működés n = 1 - P alkalmazható szereléséhez nullák minden bit információt bármely a négy detektorok P, RR, DR, ShVyh.

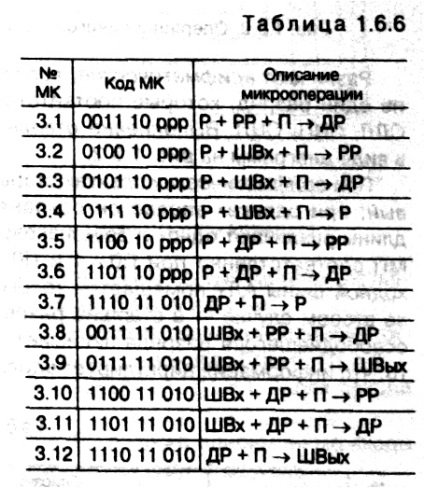

3. csoport műveletek ebben a csoportban (táblázat. 1.6.6) lehetővé teszi, hogy végre Emellett kombinálásával forrásokból (P, PP HLR ShVh) és vevők (P, PP, DR, ShVyh) információkat. Műveletek DR + P (3,7, 3,12) ténylegesen továbbítással és kiegészíti a működése 1. csoport, megengedve, hogy a növekmény a tartalmát az extra HLR.

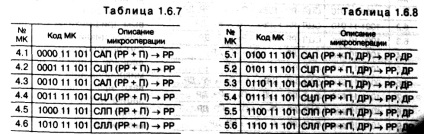

Csoportok a 4. és 5. Ezek a műveletek (táblázat. 1.6.7 és 1.6.8), képes felismerni egy komplett tartalom műszakban dolgozó regiszter (RR), vagy dupla hosszúságú regiszter (RR, DR), amely egy sorba kapcsolt PP és DR. Az utóbbi esetben lehetséges igazítás eltolódás podsummirovaniem P RR átviteli jel.

Különbséget aritmetikai, logikai és körkörös jobbra tolódik, és balra egy kicsit, amelyek rendre van elnevezések: SAP, SAL, DES, a SOM, SCP, SCL. A teljesítmény az egyes műveletek eltolódások szemlélteti a grafikonok ábrán. 1.6.2.

Az aritmetikai eltolja legrégebbi (balra) bitet használunk, mint egy mérföldkő; A jobbra tolódása mentésre kerül. Amikor dolgozik egy dupla hosszúságú operandusok különböztetni egy- és kétjegyű eltolódásokat végre a magas pozícióban, illetve az MP P0 és P0 = 1 = 0. Az első esetben, a legnagyobb helyi értékű bit az ALU kimeneti busz kerül csak az MSB a munkaidő nyilvántartás RR, a második esetben - a MSB az RR és DR. A logikai műszakban kisülés jön létre felszabadult nulla. Ciklikus műszakban jellemző, hogy az információ kering mentén nyilvántartások nélkül hagyva őket.

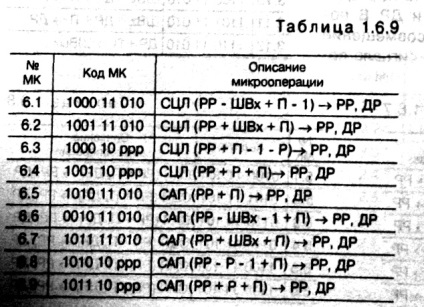

6. csoport műveletek ennek a csoportnak (táblázat. 1.6.9) lehetővé teszik, hogy végre hozzáadásával vagy kivonásával, az aktív átviteli jel P, párosulva a jobbra vagy aritmetikai maradt eltolódás jön gyűrűs regiszter RR dupla hosszúságú DR Ezek a mikro-műveletek hatékony végrehajtása érdekében, a bináris szorzás és osztás algoritmusok számokat.

Ajánlom ezt a cikket másoknak!