Közvetlen memória hozzáférés vezérlő

Közvetlen memória hozzáférés megszervezése

Közvetlen memória hozzáférés vezérlő KR580IK57 (KR580VT57)

A vezérlő programozásának sorrendje

Közvetlen memória hozzáférés megszervezése

Az adatok cseréje a VU-val a közvetlen memória hozzáférés (DMA) üzemmódban történő cseréje. Ebben a módban a VU és a mikroszámítógép fő memóriája közötti adatcsere a processzor részvétele nélkül történik. A DMA módban történő átváltást nem a processzor által végrehajtott program, hanem a processzoron kívüli elektronikus áramkörök vezérlik. Jellemzően a DMA üzemmódban lévő adatcserét szabályozó sémákat egy speciális vezérlőbe helyezzük, amelyet közvetlen memória hozzáférés-vezérlőnek nevezünk.

Adatcsere DMA mód lehetővé teszi a nagy sebességű mikroszámítógép külső tárolóeszközök, például merevlemezek, mágneslemez, hiszen a PDP nyújthat egy időben megosztás egy bájt adatot a memória és a HEV egyenlő memória-hozzáférést ciklust.

A "hurokfogás" kétféle közvetlen memória hozzáféréssel rendelkezik. A DMA legegyszerűbb módja a CPU-ciklusok azon csereprogramok használata, amelyekben nem cseréli az adatokat a memóriával. Ilyen ciklusokban a DMA vezérlő képes adatokat cserélni a memóriával, anélkül, hogy a processzor működését megzavarná. Mindazonáltal szükség van az ilyen ciklusok elkülönítésére úgy, hogy nincs átmeneti átfedés az RDP cseréjében, a processzor által indított cserélési műveletekkel. Egyes processzoroknál speciális vezérlőjelet generál, jelezve azokat a ciklusokat, amelyekben a processzor nem fér hozzá a rendszer interfészhez. Ha más processzorokat használunk az ilyen ciklusok elkülönítésére, akkor a PDP vezérlőkön speciális szelekciós áramköröket kell alkalmazni, ami megnehezíti azok tervezését. Az eljárás alkalmazása szervezet tárgyalt RAP nem csökkenti a teljesítményt a személyi számítógépek, de ebben az esetben csere DMA módban csak akkor lehetséges, véletlenszerű időpontokban Egyetlen bájt vagy szó.

Több közös van a DMA a „capture ciklus”, és a kényszerű leállítása a processzor rendszer interfész busz. Hogy végre egy ilyen rendszer DMA interfész mikroszámítógép-rendszer egészíti ki két sor vezérlőjel-továbbítás „követelménye direkt memória elérés” (TPDP) és a „rendelkezésre bocsátása direkt memória elérés” (CNDO).

A TPR vezérlőjelét a közvetlen memória hozzáférés szabályozó képezi. A processzor, miután megkapta ezt a jelet, felfüggeszti a következő parancs végrehajtását, anélkül, hogy várakozásba venné annak befejezését, kiadja a rendszer interfészének a PPDU vezérlőjelét, és lekapcsolódik a rendszer interfész buszaiból. Ettől kezdve a rendszer interfész összes buszát a PDP vezérlő vezérli. A DMA vezérlő a rendszer interfész busz segítségével egy bájtot vagy adatszót cserél a mikroszámítógép memóriájával, majd eltávolítja a TTP jelet, és visszaadja a rendszer interfész vezérlését a processzorhoz. Miután a DMA vezérlő készen áll a következő bájt kicserélésére, akkor ismét megragadja a processzor ciklusát stb. A TTP jelek közötti intervallumokban a processzor továbbra is végrehajtja a program utasításait. Így a program végrehajtása lelassul, de kisebb mértékben, mint amikor a megszakítási módban történik.

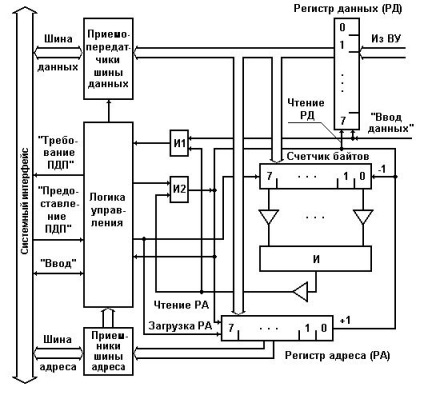

Egy egyszerű PDP-vezérlő blokkdiagramja, amely adatokat szolgáltat egy mikroszámítógép memóriájába a VU kezdeményezésére a "Capture cycle" üzemmódban, az 1. ábrán látható. 1.

Ábra. 1. A DMA-vezérlő a VU-ból a "Capture cycle" üzemmódba történő adatbevitelhez és a processzor leválasztásához a rendszer interfész buszjáról

Egy egyszerű DMA vezérlő példáján keresztül csak a vezérlő előkészítésének folyamatát tekintettük, és az adatokat közvetlenül DMA módban továbbítottuk. A gyakorlatban a DAP módban a VU-val történő adatcsere minden munkamenetét mindig a processzor által végrehajtott program kezdeményezi, és a következő két lépést tartalmazza.

1. A felkészülés a következő ülésen JE központi processzor mód, program-vezérelt csere lekérdezi az állam TDM (ellenőrzi, hogy hajlandó megosztani), és küld egy UW csapat képzést a szolga csere. Az ilyen képzés korlátozott lehet, például, amíg a fejek a kívánt zeneszámot a merevlemez-meghajtót. Ezután a letöltési DMA vezérlő regiszterek. Ebben felkészülés cseréjét a DMA mód befejezése és a CPU, hogy végre más programot.

2. Az adatcsere az RAP üzemmódban a JE előkészítő műveleteinek befejezése után kezdődik, akár a VU kezdeményezésére, akár a fentiekben említettük, vagy a processzor. Ebben az esetben a PDP-vezérlőt ki kell egészíteni egy állapot- és vezérlőregiszterrel, amelynek tartalma meghatározza a PDP vezérlő működési módját. A nyilvántartás egyik bitje a VU-val történő adatcserét kezdeményezi. A PDP vezérlő státuszának és vezérlésének nyilvántartásba való betöltése programozottan történik.

A legelterjedtebb a közvetlen memória hozzáférés módja a processzorzárással. A DAP-tól különbözik a "hurokfogás", mivel a rendszerinterfész vezérlése nem átváltásra kerül a DMA vezérlőhöz egy bájt, hanem az adatblokk cseréje idején. Ilyen DMA módot alkalmaznak olyan esetekben, amikor a VU-ból érkező egy byte átváltási ideje hasonló a rendszerbusz-ciklushoz.

Mikroszámítógépen több VU működik a DMA üzemmódban. Az ilyen buszbusz-rendszer interfészének adatcsere biztosítása prioritási alapon történik. Prioritások Slave végre, ugyanúgy, mint az adatcsere a megszakítási mód, de ahelyett, hogy a vezérlőjelek „követelmény megszakítások” és a „megszakítás Rendering” jeleket használja „követelménye a közvetlen hozzáférés” és „közvetlen hozzáférést biztosít”, ill.

Közvetlen memória hozzáférés vezérlő KR580IK57 (KR580VT57)

A processzor klasszikus konstrukcióval kezeli a számítógép adatcseréjét. Azonban olyan problémát, mint adatkommunikációt perifériák (pl. E. kommunikáció a külvilággal) megpróbál végre lehet hajtani olyan speciális információcsere eszközök. Ez lehetővé teszi, egyrészt, hogy engedje el a processzor (valamint a programozó), hogy ezt a feladatot, a másik -, hogy a szükséges adatcsere gyorsabb ütemben, mint amilyen lehetett volna feldolgozására. Végül is a perifériák a processzor sebességével összehasonlítható sebességgel képesek dolgozni. Az ilyen eszközök közé tartozik például a kijelzővezérlő vagy a rugalmas vagy merevlemezes lemezek meghajtói. Mindegyikük szükség rendszer úgynevezett vezérlő, közvetlen memória-hozzáférés, amely lehetővé teszi, hogy a processzor cserélni, és megszervezi a gyors és közvetlen adatcsere a memória és a periféria megadott.

A BIS DSP használata jelentősen csökkenti a hardver költségeit a közvetlen memória elérésében.

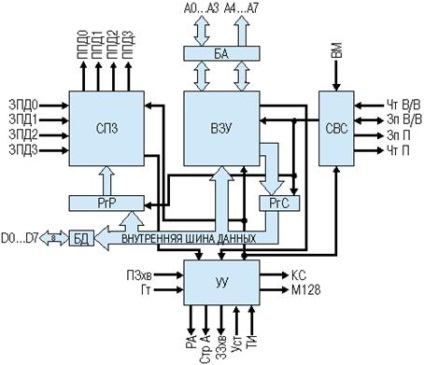

Az 1. ábrán. A 2. ábra a KR580IK57 szerkezeti rajzát mutatja a 2. táblázatban. 1-tűs hozzárendelés.

Ábra. 2. A KR580IK57 mikroáramkör szerkezete

Táblázat: Pin assignment

Az SDR-kérelmek fogadására szolgáló rendszer a nem szinkron jelek vételére és kötésére szolgál, négy eszközről a memóriához való közvetlen hozzáférés megszervezésére irányuló kérelmekről, valamint a megerősítő jelek kiadásáról. A négy csatorna mindegyike összekapcsolódik az LSI BDP-vel külön kérések sorával és a közvetlen hozzáférés megerősítésével. A megfelelő csatorna megerősítő válaszának kiadása a prioritás függvényében történik.

A vezérlőkör ciklusai során végzett műveletek sorrendjét a vezérlőegység vezérlőegysége vezérli.

Felvétel generáló áramkör, olvasás SHS kap, alkotó és kiállító jelek biztosítása közötti információcsere a processzor és a chip - az egyik kezét, és a memória és a periféria - a másikon.

RGR telepítési mód regiszter információt tárol az üzemmódok BIS, amely magában foglalja az „Indítás”, „End-stop számla”, „Extended Entry”, „Normál Rögzítés”, „prioritás Rotate” és a „fix prioritás”.

A PrP rendszerint a PrA és a Pr2 beállítás után kerül betöltésre, és a Set Set (Set) beállításával visszaállítja.

0 kisugárzás. 3 PrP engedélyezi a megfelelő csatorna működését. A 4. 7-es kisülések biztosítják az LSI megfelelő működési módját. Tehát, ha a 4Pgr bitben "1" -t rögzít, az egyes csatornák prioritása megváltozik.

A kiszolgált csatorna lesz a legalacsonyabb prioritás. A csatorna karbantartás sorrendje a 0 >> 1> 2> 3> 0 számnak megfelelő. Ha a 4 PrP bit értéke "0", akkor minden csatornának fix prioritása lesz. Tehát a 0-as csatornának van a legmagasabb prioritása, és a 3. csatorna - a legalacsonyabb prioritás. Ha az "1" az 5. PrP-re van írva, akkor a "Bővített felvétel" mód van beállítva. Ebben a módban a ZpP és a Zn V / V jelek időtartama akkor növekszik, ha nincs kész jel a külső eszközről. Ebben az esetben az LSI belép a várakozási állapotba.

Ha az "1" a 6. PrP-re van írva, a "Számlázási várakoztatás vége" üzemmód van beállítva. Ebben az esetben a CS jel megjelenése után a kiszolgált csatorna tilos. Ha továbbra is szükséges a csatorna karbantartása, annak felbontási bitjét újra kell programozni. A Prg bitben a "0" -nál a CS jelének megjelenése nem tiltja a csatorna ismételt szervizelését.

A PrP 7. kategóriájában az "1" kategóriában állítsa be az "Üzembe helyezés" módot, így a 2. csatorna ismételten átugorhatja az adatbázist, vagy többféle tömböt kapcsolhat össze szoftveres beavatkozás nélkül.

Beprogramozza csatorna 3 információkat tárolja, hogy állítsa vissza a csatorna regiszter 2. továbbítását követően a blokk jel KS és a megjelenése a tartalmát csatorna regiszter 3 átkerül a megfelelő regiszterek csatorna 2. Amennyiben regiszterek a csatorna 2 van egy „helyettesítés” adatcsatorna jegyzék 3, meghatározott mentesítés „adatok frissítése zászló” a csatorna állapot regiszter.

A PgC csatornaállapot-regiszter azt a csatornaszámot jelöli, amely elérte a számlálás végét. Ezenkívül a PrgS tartalmazza a fent leírt "Data update flag" bitet.

A művelet részeként a mikroprocesszor chip rendszer lehet az alábbi állapotok: a kezdeti programozási várakozások szolgáltatás.

A kiindulási állapotban chip szüksége van a külső jel Const. Ebben az állapotban az összes kérés elfedi PD csatornák és pufferek A0. A3 átkerülnek a vételi állapot információt. Az állami MP programozási hozzáfér a belső regiszterek a kiválasztott csatorna táblázat szerint. A 2. és 3..

A készenléti állapot egy chip végétől a programozási kimeneti fordulatszám jel, vagy a ciklusok között PD.

Kézhezvételét követően a jel MP jelenlétében PZhv kérelem jelet chip és egy jelet generál PDI bemegy szolgáltatást, ahol a rendszer busz ellenőrzése alatt LSI RAP.

A3 A2 A1 A0 Működés Regisztráció

0 0 0 1 0 Sn csatorna, a ciklusok számát

0 1 1 0 Sn csatorna 1, a ciklusok számát

0 1 0 1 2-es csatorna Sn, a ciklusok számát

1 1 1 0 Sn Channel 3, a ciklusok számát

1 0 0 0 Cs CSG Reading

1 0 Sn 0 0 Írásban WGR

A szekvencia vezérlő programozási

Programozás megkezdéséhez a WGA és sGC kiválasztott csatorna (vagy a kiválasztott csatorna).

Minden. Most DMA ciklikusan küld egy memória területet 76D0H-7FF3H a kijelző vezérlő, megállt ebben az időben a processzor.

Minden anyag a „tudomány”