Építészet FPGA (FPGA)

FPGA - rövidítése az angol kifejezés mezőprogramozható kaputömbbel.

FPGA - rövidítése az „programozható logikai integrált áramkörök”. A szó előfordul az FPGA orosz dokumentáció és leírások az FPGA szavak helyett. FPGA - a továbbiakban általában ezt a kifejezést használjuk.

PLD és FPGA - a rövidítése az azonos osztályú elektronikus alkatrészek, chips. Ez a chip létrehozásához használt saját digitális integrált áramkör felépítését.

FPGA működése határozza meg nem a gyártó chip gyár, és további programozás (mezőn programozható) segítségével speciális szerszámok: programozók és szoftver.

FPGA chip - nem ez a mikroprocesszorok, amelyben a felhasználói program végrehajtása egymás után, a csapat mögött a csapat. A FPGA megvalósított elektronikus áramkör, amely a logika és a flip-flopok.

Draft FPGA lehet tervezni, például, mint egy kapcsolási rajz. Mégis, vannak speciális leíró nyelvek Verilog VHDL vagy hardver típusát.

Mindenesetre, grafikus és szöveges leírást a projekt megvalósítja digitális elektronikus áramköröket, amely végül „beágyazott” az FPGA.

Általában az FPGA chip is áll:

- konfigurálható logikai blokk, hogy hajtsák végre a kívánt logikai funkciót;

- programozható elektronikus közötti kapcsolatok konfigurálható logikai blokk;

- programozható I / O blokkok, amely összeköttetésben van a külső kimeneti chip belső logikája.

Szigorúan véve ez a lista nem teljes. A modern FPGA gyakran beágyazott kiegészítő memória blokkok, DSP blokkok vagy szorzó, PLL és egyéb alkatrészek. Itt, azt nem kell figyelembe venni ezt a cikket.

A projekt fejlesztője FPGA általában elvonatkoztatott a belső szerkezete egy adott chip. Egyszerűen írja a kívánt logikája „saját” jövő a chip a diagram formájában, vagy a szöveg a Verilog / VHDL. Compiler ismerve a belső szerkezetét FPGA maga kívánja elhelyezni az áramköri eszköz a rendelkezésünkre álló konfigurálható logikai blokkok és próbál kapcsolódni ezeket a blokkokat meglévő programozható elektronikus kapcsolatokat. Általában az elhelyezés és routing közötti kapcsolatok logikai blokkok az FPGA a fordító.

Osztályozás FPGA konfiguráció tároló típusú.

SRAM-alapú.

Ez az egyik leggyakoribb típusú FPGA. FPGA konfiguráció van tárolva egy statikus memória sejtek gyártott standard CMOS technológiával.

Az előnye ennek a technológiának - a lehetőséget, több átprogramozása FPGA. Hátrányok - nem a legnagyobb teljesítményt, miután a firmware el kell látni újra a feltöltést. Tehát a tábla még állni rakodó, speciális chip FLASH vagy mikrokontroller - mindez növeli a költséget a végtermék.

Flash-alapú.

Az ilyen konfiguráció, tároló chipek fordul elő a belső memóriában vagy FLASH EEPROM típusú. Ezek FPGA jobb, hogy a készülék ki van kapcsolva firmware nem vész el. Bekapcsolás után chip ismét üzemkész. Azonban az ilyen típusú FPGA megvannak a maga hátrányai. Végrehajtása FLASH memória belsejében CMOS chip - ez nem túl könnyű. Ez szükséges, hogy összekapcsolják a két különböző technológiai folyamat a termelés az ilyen chipek. Tehát ezek drágábbak. Ráadásul ezek a forgácsok hajlamosak arra, hogy korlátozott számú írási ciklust konfigurációt.

Antifuse.

A speciális technológiával hajtják végre egyszer programozható FPGA. Programozása FPGA szétolvad a megfelelő helyen külön chip jumper, így a kívánt áramkört.

Hátrány - a tényleges program / flash chip csak egyszer. Ezt követően, semmit sem lehet korrigálni. piercing folyamat önmagában nem elég gyors. De nagyon sok előnye van az ilyen FPGA: ezek elég gyors (működhet magas frekvenciák), kevésbé hajlamosak a meghibásodásra besugárzása alatt - minden annak a ténynek köszönhető, hogy a konfiguráció formájában kapjuk a hidak, nem a formában további logika, mint az SRAM-alapú .

Konfigurálható logikai blokk.

A dokumentáció Altera közös expressziós Logic Array blokk (LAB) - egy sor logikai. A Xilinx FPGA chipek a cég megközelítőleg azonos egységek - konfigurálható logikai blokk (CLB). A konfigurálható logikai blokk - alapvető eleme a FPGA, van néhány egyszerű logikai függvény érvényesítése, illetve a számítás eredménye a tároló regiszterek (flip-flop) végezhető.

A komplexitás és szerkezetét a konfigurálható logikai blokk (CLB) határozza meg a gyártó.

Elméletileg, a konfigurálható logikai blokk lehet, például nagyon egyszerű, csak mint egy tranzisztor. Vagy lehet, hogy nagyon nehéz, mint a processzor. Ez a legtávolabbi pont a megvalósítás.

Az első esetben, szüksége van egy hatalmas számú programozható linkeket, hogy majd az egyes tranzisztorok gyűjteni a szükséges rendszert. A második esetben a link nem kell annyira, de elvesztette a rugalmasságát egy egyedi kialakítású rendszer.

Ezért konfigurálható blokk általában egy valami a kettő között: általában elég bonyolult ahhoz, hogy varrt a funkció, de elég kicsi ahhoz, hogy befogadja a több blokkból belül FPGA és képesek összekapcsolni őket egy egységes rendszer.

Így a választás egy konfigurálható logikai blokk felépítése az FPGA gyártó - ez mindig a kompromisszumra a kocka területén, a sebesség, az energiafogyasztás és így tovább.

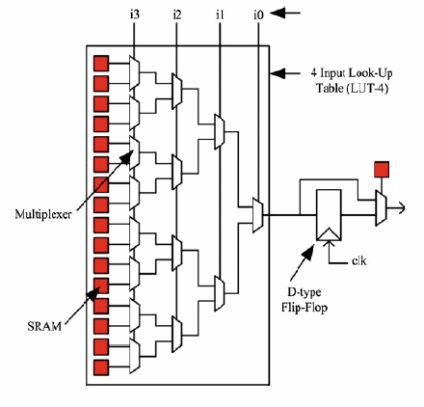

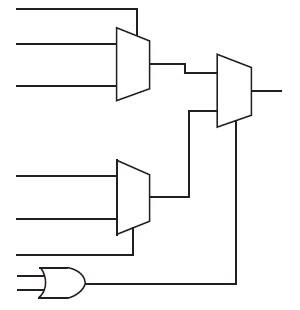

A konfigurálható logikai blokk állhat egy vagy több alapvető logikai elemek. Az angol irodalomban ezt Basic Element Logic (BLE), vagy egyszerűen logikai elem (LE). A FPGA általánosan alkalmazott úgynevezett alap LUT-alapú logikai elemek. Valami ehhez hasonló:

Ábra. 1. példa a hagyományos bázikus logikai elem.

LUT - ez Look-Up Table, LUT. Például, az 1. ábra négy bites LUT tagjai alapvető logikai blokk. Itt a négy szám a bemenet logikai funkció társul egy bites eredményt. Vörös négyzetek ábrán. 1 jelöli a programozható elem indexet - ez a memóriát, ahol a FPGA firmware van tárolva. Látható, hogy a konfiguráció egy 4-bites LUT igényel 16 konfigurációs regiszterek. A tartalom az e nyilvántartások adja meg a logikai függvény belül végrehajtott alap logikai elem.

Egy másik konfigurációs regiszter (ábrán. Az 1. ábra egy egyetlen piros négyzet jobbra) meghatározza, hogy a kimeneti alap logikai kaput kibocsátó közvetlenül az értéket LUT vagy kibocsátandó beírható D-flip-flop egy értéket LUT. Freeze adatok tárolására és digitális áramkörök szükség szinte minden projektben.

Tekintettel ábra. 1 példáján a hagyományos alap logikai elem megérteni, mi redundancia építeni a kristály modern FPGA (SRAM-alapú). Miután az összes, sőt, a konfigurációs regiszterek (piros négyzet) közvetlenül nem áll rendelkezésre használható digitális projektben. Ezek csak arra szolgálnak, hogy egy felhasználói függvény. Egy D-flip-flop a felhasználói projekt szükséges több mint 16 (néha több) flip-flop tárolására FPGA konfiguráció.

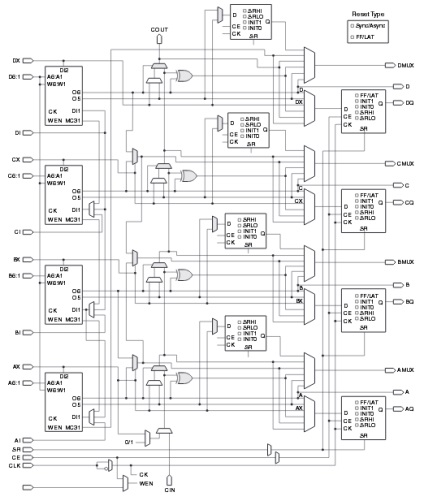

Tény, hogy egy alap logikai elem különböző FPGA sokkal bonyolultabb, mint ábrán látható. 1. Íme néhány példa a dokumentáció különböző típusú FPGA.

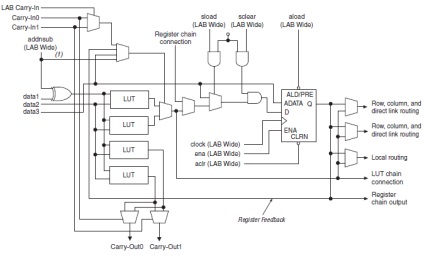

Ábra. 2. Az alap logikai elem CPLD MAX II Altera.

Vannak jól látható és a D-LUT tároló kiváltó eredményt. Az alábbiakban látható. A 3. ábra az alapelem Cyclone III.

Ábra. 3. Base kapu FPGA Cyclone III Altera Company.

Az Altera chipek egy LAB tartalmazhat 10-16 LE.

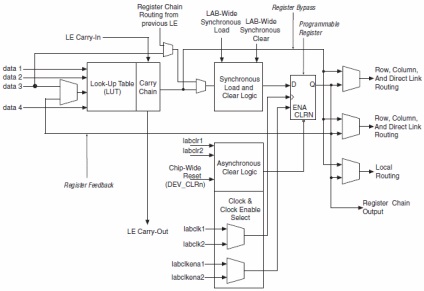

A chipek a Xilinx Virtex-6 bázis kapu - az úgynevezett szelet. Egy CLB csak két szelet. De egy szelet - ez egy elég bonyolult szerkezet:

Ábra. 4. Az alaptag 6 Xilinx Virtex-szelet.

Egy CLB Virtex-6 8 LUT 16 és D-kiváltó és valami mást, plusz ehhez. Azért, mert ez bonyolult.

A másik véglet - chip FPGA Microsemi cég (korábban Actel).

Például egy sor chips 40MX alapvető logikai elem a következőképpen néz ki:

Ábra. 5. logikai modulja Microsemi 40MX sorozat.

Nyolc bemenettel és egy kimenettel.

Nincs olyan Look-Up Table, vagy akár egy D-flip-flop. Trigger, mint a többi logikai forma, ahol van, hogy mint ezek az apró építőkövei - logikai modult.

Miért különböző cégek volt olyan nagy különbség a végrehajtása az alapvető logikai kapu? Úgy tűnik Microsemi chipek közötti kapcsolat alapegységek sokkal olcsóbb: 40MX sorozat egyszeri programozható. Ez köti össze a kommunikáció „elolvadt” között az összekötő utak és később nem módosítható. Nincsenek nyilvántartások átmenetileg tároló firmware. Nincs programozható kapcsolók, multiplexerek, mint a más típusú FPGA. Tehát chip vállalatok Microsemi - ez kissé speciális eset. Ez a technológia az úgynevezett antifuse - a termelés chipek egy módosított CMOS gyártási technológia és a további rétegeket szervezni összekapcsolási linkek.

Programozható közötti kapcsolat logikai blokkokat.

Az FPGA szerzett nekünk a kívánt digitális áramkör nem elég, akkor be kell állítani a rendelkezésre álló logikai blokkok különleges módon, továbbra is szükség van, hogy hozzon létre, a program közötti kommunikáció logikai blokkok.

Erre a célra vannak speciális FPGA-konfigurálható kapcsolókat.

Az angol nyelvű dokumentációban az alábbi feltételekkel: FPGA Routing Architektúra és programozható Routing Interconnect. Ez az egész arról, hogy a kapcsolatok a programozható logikai tömbök.

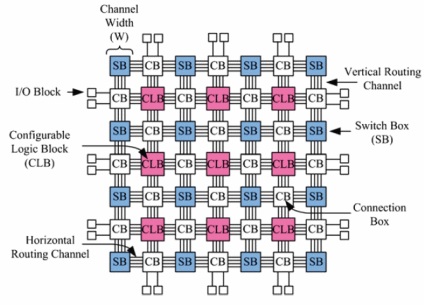

Két alapvető módszerek épület típusától FPGA architektúra linkek: szigetei és hierarchikus.

Ábra. 6. Island FPGA.

Island FPGA úgynevezett mert konfigurálható blokkok mind egyenlők egymással, és olyanok, mint szigetek a tengerben, kapcsolási csomópontok között és linkek.

Itt látható. 6. kijelölt CB - Csatlakozó Doboz és SB - Switch Box. Lényegében ez a programozható multiplexerek, hogy csatlakoztassa az egyik vagy másik CLB CLB másik keresztül vezetékek láncok egy FPGA.

Ez a sziget-stílusú FPGA vagy háló alapú FPGA. Egy tipikus példa az ilyen chipek - egy sor Altera Cyclone és Stratix.

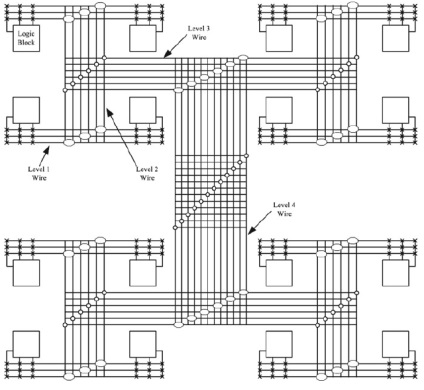

Egy második ismert típusú FPGA - egy hierarchikus FPGA. Itt van egy számítást, hogy az áramkör mindig területeket, amelyek kölcsönhatásba lépnek egymással szorosabban, mint a távoli modulok a design.

Ábra. 7. Hierarchikus FPGA.

Itt a közelben CLB csatlakozni nagyon egyszerű, nem kell egy csomó kapcsolók és a kapott csatlakozás gyorsabb. De ha van egy nagyobb blokk számológépek, a jel, hogy elérje a magasabb szintű hierarchia, majd jött beljebb a következő „szoba”.

Nem mondhatjuk, hogy sokkal rosszabb, mint a sziget-szerű. Csak minden módszernek vannak előnyei és hátrányai.

Tipikus képviselői hierarchikus FPGA - egy chip vállalat Altera sorozat Flex10K, APEX.

Szoftver tervezése FPGA.

Szoftver tervezése FPGA, nevezetesen fordító (logikai szintetizátor és Fetter szerelő) - talán a legnehezebb része az egész FPGA technológia.

A fordító meg kell vizsgálnia a felhasználói program (ábrák és szöveges leírások Verilog HDL vagy VHDL), és létrehoz egy hálójegyzékkel (hálójegyzékkel) - a lista az összes áramköri elemeket és kapcsolatokat közöttük. Netlist optimalizálni kell - logikai függvények minimalizálása szükséges esetleges kétszeres nyilvántartások törölni.

Akkor a fordító tartalmaznia kell minden logikáját kötéslistában a meglévő architektúra az FPGA. Ez teszi Fetter (szerelő). Úgy teszi logikai elemek és végrehajtja felkutatására a köztük lévő kapcsolatok (hely és útvonal folyamat). A nehézség abban rejlik, hogy egy és ugyanaz a projekt lehet helyezni az FPGA sok szempontból, és ezeket a módszereket milliók. Az elhelyezés és routing jobbak, mint mások. A fő minőségbiztosítási rendszer kapott kritérium - a maximális frekvencia, amelyen a projekt képes lesz együtt dolgozni ezzel a telepítési elem és egy adott nyomot kapcsolatokat. Itt érinti kötéshossz közötti logikai blokkok száma és a programozható kapcsoló közöttük.

Compiler tudva FPGA architektúra teljesítmény problémák további jelentést a folyosón órajeleket regiszterből regisztrálni. Ez az információ gyakran hasznos, ha egy fejlesztő nagy teljesítményű rendszerekhez. Fejlesztő FPGA képes adni néhány tanácsot, hogy a fordító, ahol ahol a kristály jobb hely egy különleges kialakítás egységet.

Kiválasztása a projekt, a sajátos kártya chip FPGA fejlesztő kap egy bizonyos mértékig attól függően, hogy a gyártó az FPGA, akárcsak a szoftver használatát az azonos gyártótól.

Szoftver vállalatok Altera: Quartus II.

Xilinx szoftver tervezése FPGA: ISE lakosztály, Vivaldo Design Suite.

A cég szerint Microsemi: Libero IDE, Libero SoC.

Talán szoftver fordítóprogramok FPGA - a legfontosabb eleme a szellemi tulajdon cégek FPGA gyártók.