65 nm-es gyártási technológia - a közeljövőben félvezető technológiák intel

Köszönjük a támogatást!

A jelenlegi állapot a félvezető technológia Intel 90 nm-es gyártási technológia

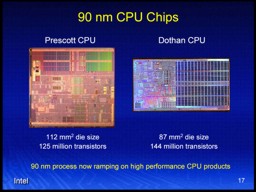

Először is, a hangsúly a jelenlegi állapot a vállalat területén a félvezető és a mikroprocesszoros technológia, az új 65 nm-es gyártási technológia nagyrészt fejlesztés a megtestesült ötletek megvalósítása a jelenlegi generációs 90 nanométeres mikroprocesszorok. Tehát, felsoroljuk a legfontosabb pontjai a modern 90 nm-es technológiával.

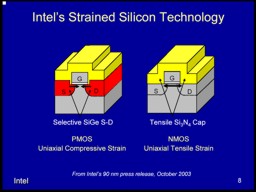

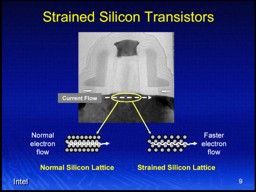

1. A feszült szilícium technológia

Talán ma már a legismertebb a „tömegek” technológia különbözteti meg az Intel 90 nanométeres eljárással a korábbitól. Célja, hogy a megoldása az egyik legfontosabb feladat a mikroprocesszor ipar # 151; sebességének növelése a tranzisztorok alkotó processzormag. Ennek elve abban áll, nyújtás (abban az esetben, NMOS tranzisztorok) vagy kompressziós (a PMOS tranzisztorok) szabályos kristályos szilícium rács # 151; anyag csatornás FET, amelyek növekedéséhez vezet elektron-lyuk vezetőképesség, azaz gyorsul a rajta átfolyó villamos áram segítségével a csatornán csökkentésével ellenállás (akár 30% a PMOS-tranzisztor, és a 10% -ban NMOS-tranzisztorok). Az viszont, ezzel is növelve a kapcsolási sebessége a tranzisztorok, amelynek eredményeként a végleges formáját a lehetőségét, hogy növelje a processzor sebességét (feltételezve, hogy a mikroprocesszoros mag egy CMOS-oldatot, azaz kombinációja PMOS és NMOS típusú-tranzisztorok, az átlagos kell számítani, hogy 20% a növekedés). A kompressziós vagy húzó szilícium rácsszerkezet megfelelő általában a „feszültség”, amely tükrözi a cím ennek a technológiának.

feszült szilícium technológia Intel. balra # 151; kondenzált kristályrács szilícium tranzisztor és PMOS-feszített kristályos szilícium rács NMOS-tranzisztorok; jobb # 151; átfolyó áram a jobb és a kemény kristályos szilícium rács.

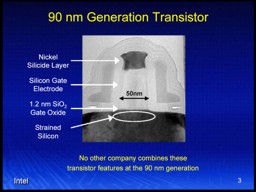

2. Jobb tranzisztorok

Egy lényeges komponense a 90 nm-es folyamat Intel a használata a miniatűr, nagy teljesítményű tranzisztorok, amelyek egy alacsony energiafogyasztás és a műveleteket csökkentett tápfeszültség (

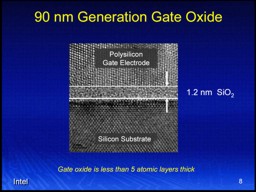

1.2). Characterized tranzisztorok 50 nm vastag kapu poliszilícium gyártott bevonatokkal nikkel szilicid (NiSi) # 151; olyan anyag, amelynek a kisebb lineáris elektromos ellenállás, összehasonlítva a korábban alkalmazott kobalt disilicide (CoSi2) a következő területeken: a kapu hossza kisebb, mint 100 nm. A vastagság a dielektromos-oxid réteg egy kapu a 90 nm-es tranzisztor 1,2 nm, az utóbbi anyaga hagyományos szilícium-dioxid (SiO 2), ami jól működik az elmúlt 30 évben, mint egy anyag a komponens tranzisztorok elsősorban a könnyű gyártás (-oxid réteget közvetlenül „in situ”, azaz a gyártási folyamat során a tranzisztorok, termikus oxidációja a szubsztrátum felületének). Ezen túlmenően, a használata ez az anyag lehetőséget nyújt a további növelésével a művelet sebessége tranzisztorok által képzett vastagságának csökkentésével a szigetelő őket (természetesen csak egy bizonyos határig, az alábbiakban tárgyalt).

90nm tranzisztorok. balra # 151; perspektivikus nézete tranzisztorok; jobb # 151; egy kapu-oxid réteg.

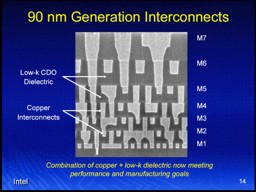

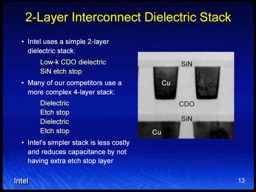

3. 7-rétegű mezhtranzistornye vegyületet

A találmány szerinti eljárás magában foglalja a 7-rétegű réz összekapcsolási nagy sűrűségű, ami alacsonyabb a teljes gyártási költség, valamint egy új típusú dielektromos alacsony dielektromos állandójú (alacsony-k), amely egy szilícium-nitrid (SiN) kombinációban egy oxid anyag ( a pontos összetétele, amelyek nem kerülnek nyilvánosságra), adalékolt szén (szénnel adalékolt oxidot, CDO). Ez csökkenti „Intercontact” kapacitás 18-20% képest az alkalmazott 130 nm-es szilícium-oxid-fluorid (SiOF), amely gyorsítja a „vnutrichipovuyu” kommunikáció és csökkenti a fogyasztást a chip.

90nm mezhtranzistornye vegyületet. balra # 151; általános formája a vegyületek; jobb # 151; a szerkezet a dielektromos réteg.

4. 300 mm-es hordozó gyártási

Mikroprocesszoros mag által termelt 90 nanométeres technológiával.

Közeljövőben félvezető technológiák Intel 65 nm-es gyártási technológia

1. Egy javított feszített szilícium technológiát

feszített szilícium alkalmazott technológia Intel fentiekben tárgyalt kiindulva 90 nm-es eljárással, a 65 nanométeres technológia lesz annak továbbfejlesztését. Alkalmazása révén egy erős technológia „feszültség” szilícium csatorna, egy új folyamat elért további növekedése sebesség kapcsolási tranzisztorok által aktivitásának növelésével a jelenlegi (ID. Vagy ionja) 10-15%, miközben lényegében állandó szivárgási áram a kapun oxidréteg (iGate). A teljes nyereség az órajel eredményeként a javított második generációs feszített szilícium technológia szerint az Intel, az a 30% nagyságrendű (szemben a „hangsúlytalan” szilícium).

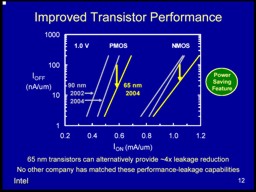

2. Új 65nm tranzisztorok

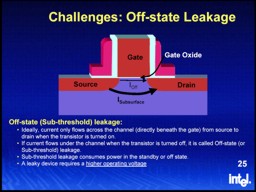

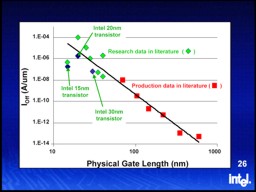

Tranzisztorok koholt a 65 nm-es gyártási technológia, azzal jellemezve, hogy tovább csökkenti a nikkel sziliciummal poliszilícium kaput hossza 35 nm, miközben a vastagsága a kapu-oxid réteg 1,2 nm. Ez utóbbi körülmény az oka a szivárgási áram védelmi ugyanazon a szinten, és ezek kombinációja tények csökkentik a kapu kapacitás (CGate) legfeljebb 20%, ami csökkenéséhez vezet fogyaszt chip „aktív” teljesítmény. Mindazonáltal nem szabad elfelejteni egy ilyen fontos jellemzője a FET a nyugalmi áram (IOFF) # 151; folyó áram a forrástól a Drain egy „alvó” módban tranzisztor, az előfordulása, amely kapcsolatban van a részleges „lebontás” a zárócsatorna anyag és a szubsztrátum anyag. A legutóbbi bemutatása 65 nm-es technológiával nem talált semmilyen említést erről, elég alapvető pont, hanem, mint kiderült, a bemutatott rajzok IOFF csak ... észrevétlenül helyébe az értéke iGate. Ugyanakkor, az irodalomból is jól ismert, hogy csökkenti a kapu hossza szükségszerűen együtt jár növekedése a jelenlegi IOFF. amely egyébként nem tagadja, és az Intel maga számos egyéb előadások.

A probléma a szivárgási áram a nyugalmi állapotban (IOFF). felülről # 151; magyarázata az a probléma lényegét. alulról # 151; arány ION / IOFF 90 nm-es és 65 nm-es tranzisztor szerint az utolsó előadás 65 nm-es technológiával (balra) és a függőség a jelenlegi IOFF kapu csatorna mérete szerint a „jövő tranzisztorok” bemutatkozó Intel (jobbra). IOFF mismatch adat. kivett két különböző kiszerelésben ugyanaz a cég, mint a mondás tartja, „van”.

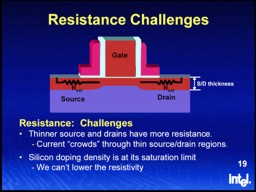

A problémát a növekvő villamos ellenállása az anyag forrás és a leeresztő csökkenő méretű. A döntés, hogy 65 nm-es eljárás képviseli, mint az alkalmazás a nikkel-szilicid (NiSi) előállítására adatok bevonó komponensek együtt tranzisztorkapu bevonattal.

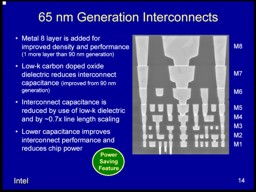

3. 8-rétegű mezhtranzistornye vegyületet

Az új eljárás is módosítja a gyártási rendszer összekötő részeihez. Először is, még egy, a nyolcadik fém- (réz) réteg képezi további növekedését érintkező-sűrűség és a terjedési sebesség az elektromos jelek. A dielektromos még mindig használják alacsony k-oxid anyag adalékolt szén (CDO), de megállapítja, hogy a gyártási technológia már képest javult a jelenlegi 90 nm-es folyamat. Az ilyen anyagok együtt az új eljárás 0,7-szeres léptékű vonalak rézvegyületek vezet további csökkentését „Intercontact” kapacitás, amely, mint azt az előző szakaszban, ami a csökkenése disszipált mezhtranzistornyh vegyületek.

65nm-es mezhtranzistornye vegyületet. Általános nézet, és egy rövid leírást a technológia a gyártás.

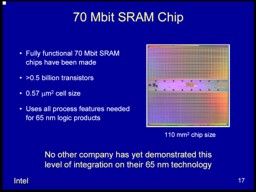

4. 2 0,57 mikronos SRAM cella tranzisztorok „alvó”

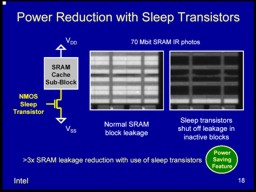

65nm-es statikus memória chipek (SRAM). balra # 151; Tekintettel a chip és jellemzői; jobb # 151; energiatakarékos tulajdonságai chip használatával kapcsolatos az „alvó tranzisztorok”

Cell 65 nanométeres SRAM-chip egy csomag hat tranzisztor (6T technológia), valamint van egy területe 0,57 m 2 (az összehasonlítás, egy 90 nm-es cache SRAM területe 6T-sejt 1,0 m 2), és az jellemzi, hogy viszonylag alacsony statikus zaj küszöb (Statikus zajhatárból SNM), amely lehetővé teszi a készülék működni feszültségig 0,7 V.

Amint azt a bemutatása a 65 nanométeres technológia fontos különbség az új 65 nm-es chip SRAM a használata úgynevezett „alvó tranzisztorok”, amelyek szabályozzák az áramot a submassivam SRAM cellák állapotától függően (tápfeszültség egy adott sejtsorozatot ki van kapcsolva, ha tétlen és benne van a gyakorlat kezelés egyik eleme a készlet). Nyilvánvaló, hogy az alkalmazásának eredményeként a „tranzisztorok alvó módba” jelentős csökkenése a villamosenergia-fogyasztás alrendszer processzor cache, ami különösen fontos a mobil eszközök. Annak ellenére, hogy ez a technológia tekinthető megkülönböztető jegye az 65 nm-es SRAM eszközökre, meg kell jegyezni, hogy ez a (nem mondjuk, hogy egy ilyen) technológiát, sőt, már régóta végrehajtani és használni, mivel a napon 130 nm-es mobil Pentium M processzorok kernel Banias, akik tudják, hogyan kell „elaltatni” kihasználatlan területeit az L2 cache.

5. 300 mm-es hordozó gyártási

A termelés 65 nanométeres chip ugyanazt a 300 mm-es ostya előállításához felhasznált a jelenlegi generációs 90 nm-es processzor magok. Kísérleti gyártás magukat 65nm eszközök most végzett a gyárban D1D Hilsbro, Oregon, ahol kifejlesztette a folyamatot.

A fő feladata a közeljövőben félvezető technológiák Intel

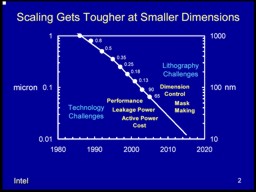

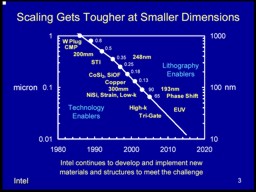

technológiai problémák

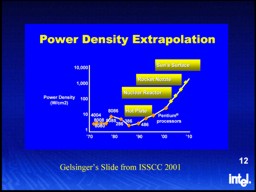

Melyek a fő technológiai kihívások kezelése félvezető technológiák? A legfontosabb, az Intel a következő elemeket: a teljesítmény (természetesen utalva a nagyobb és nehezebb, mint a kedvenc „egyre gyakrabban” vagy „törekvés gigahertz”), csökkentve a jelenlegi szivárgás problémát, és a „ára” tovább nő a hasznos teljesítmény (arányának növelésére ION / IOFF).

Trehzatvornye (tri-gate) tranzisztorok

A probléma a szivárgási áram

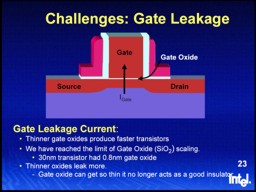

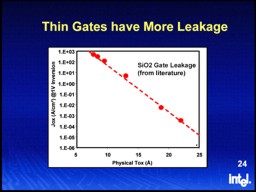

Amint azt fentebb a modern 90nm és a jövőbeli 65 nanométeres folyamatok, mint anyag a dielektromos kapu réteg a 30 éves, a szilícium-dioxidot alkalmazunk (SiO 2), elsősorban a lehetőségét, hogy növeli a tranzisztor működési sebesség csökkentésével a képződött vastagsága őket, hogy a szigetelő réteg. Azonban, további csökkentése vastagsága oxidréteg (vastagsága 1,2 nm, használt 90 nm-es, és 65 nm-es gyártási technológia, aránya mindössze 5 atomi réteg!) Elkerülhetetlenül együtt a megjelenése káros hatások, különösen a # 151; növekvő áram szivárgást a kapun dielektrikum (iGate), amely megnyilvánul, mint egy jelentős növekedése energiafogyasztás és teljesítmény disszipáció, valamint a „rendellenes” viselkedése a tranzisztor (vegye figyelembe, hogy ezek a problémák 90nm processzor Pentium 4 Prescott órajele 4,0 GHz-es és soha nem látott napvilágot, és a közelmúltban teljesen kizárni a fejlesztési tervek).

A probléma a szivárgási áram a kapun (Igate). balra # 151; magyarázata az a probléma lényegét; jobb # 151; függése szivárgási áram a vastagsága a kapu oxidréteg.

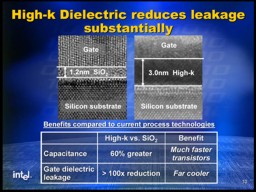

Ahhoz, hogy megoldja ezt a kritikus Intel problémát tervezik, hogy a jelenlegi anyagot a dielektromos kapu bevonat (SiO 2) egy vastagabb réteg anyag, amely magas dielektromos állandó (high-k), amelyek a jobb hőszigetelő tulajdonságokkal és létrehoz egy nagy kapacitás között a kapu és a tranzisztor csatorna (, azzal Intel, a neve «nagy k» származik csak a kifejezést «nagy kapacitású»). Az első tulajdonság az ilyen anyag nagy mértékben csökkenti a szivárgási áram, azaz fogyasztás tranzisztor „passzív” erő, és a második lehetővé teszi, hogy jelentősen növeli a kapcsolási sebessége annak államok. Előnyös magas k anyagok a szakirodalomban jegyzeteket használja a cirkónium és hafnium oxidjai.

A használat dielektrikumok nagy dielektromos állandójú (high-k) anyagot, mint a kapu szigetelő réteg.

litográfia feladat

Között a litográfiai feladatok Intel mondja jövőben a probléma nagyságát a vezérlőelem és a gyártás maszkokat. Mielőtt rátérnénk a rövid megfontolás ezeket a problémákat és azok megoldásait, középpontjában részletesebben a folyamat litográfia általában.