stream processzor

Kérdés # 2 „besorolása mikrokontroller”

Minden MC osztható három fő csoportba:

MK 8 bites beágyazott alkalmazások;

16 és 32-bites MC;

digitális jelfeldolgozó (DSP).

A digitális jelfeldolgozó (DSP) - egy speciális processzor a digitális jelfeldolgozás. Tulajdonságok: Harvard architektúra beépített véletlen hozzáférésű memória (szinkron mintavétel több gép szó), a hardver a komplex digitális jelfeldolgozás utasítást (pl szorzás-összeadás művelet: 1 ciklus), beágyazott hurok, egy meglehetősen nagy szállítószalag hossza a.

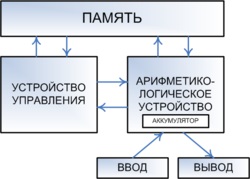

Neumann-architektúra - közös tároló programok és adatok a számítógép memóriájában (olcsóbb, de lassabb). Általánosságban:

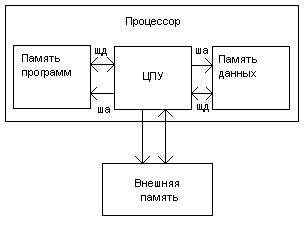

Harvard architektúra - szoftverek és adatok tárolása a különböző tárolók (a Neumann architektúra letöltésére utasítás és két operandus szükséges három lépésben, két, a valóságban ez az idő csökkenthető egy órajel ciklus).

Kérdés # 3 „Trendek a fejlesztés az építészet”

Kérdés # 5 - „Az események áttekintése áramlat ellenőrzés mikroprocesszor”

Szemszögéből a csere parancsok között a processzor és a memória az összes számítógépet lehet osztani négy osztályba:

SISD (Single Instruction Single Data) - «egyedi utasítás folyam, egyetlen adatfolyam";

SIMD (Single Instruction Multiply Data) - az egyik patak utasítások, a sok adat áramlik;

MISD (Multiple Instruction Single Data) - sok csapat árammal, egy adatfolyam;

MIMD (Multiple Instruction Multiple Data) - sok csapat patakok sok adatfolyamot.

A legáltalánosabb formája egy többszálú processzor tartalmaz két típusú primitíveket. Az első típus - olyan erőforrás, amely támogatja a végrehajtás áramlás, amely az úgynevezett mutexet (kölcsönös kizárás - «kölcsönös kizárás"), és a második - az eseményt. Azaz, mind fizikailag megvalósított egy adott mutex, attól függően, hogy a kiválasztott program - SMT vagy CMP. Mindenesetre, a végrehajtási folyamat célja annak biztosítása, hogy a következő patak zahvatyvaaet mutexek idején kivégzés, majd elengedi. Ha a mutexeket által elfoglalt egy szál, a második menet is vásárolni. A konkrét eljárást az átadása hatóság a birtokában mutexet egyik szál a másikba lehet véletlenszerű; ez függ a végrehajtását ellenőrző, például egy adott operációs rendszer. Mindenesetre, az irányítás kell építeni úgy, hogy a pénzt, amely a mutexet, elosztott helyesen és a nyomasztó hatása bizonytalan.

Események - olyan tárgyak (esemény), ez jelzi a változást a külső környezet. Ezek lefordítani készenléti üzemmódba az esemény előtt, vagy jelentse az állapotát, hogy egy másik esemény. Ily módon az események hatnak egymásra, és ahol az adatok folytonosságát biztosítani kell az események között. Végrehajtásra váró szer tájékoztatni kell a rendelkezésre álló adatok azt. És mivel a forgalmazási mutex kell szorítani a hatása bizonytalan, ezért, ha dolgozik az eseményeket kell elnyomta a hatását az ismeretlen. SMT először a program kapcsán a Compaq Alpha 21464 processzorok, valamint az Intel Xeon MP és Itanium

Nincs elegendő bizonyíték arra, hogy egyértelműen meghatározza a CMP előnyeit összehasonlítva SMT. A tapasztalat létrehozása processzorok végrehajtási SMT, sokkal nagyobb: közepe óta 80-as készült több tíz kísérleti termékek és több soros processzorok. Története CPM míg Röviden: ha nem veszik figyelembe az adott család jelfeldolgozó processzorok Texas Instruments TMS 320C8x, az első sikeres projekt a Hydra készült a Stanford Egyetemen. Között az egyetem kutatási projektek, amelyek célja, hogy kiépítsék a CMP-feldolgozók, ismert három - Wisconsin Multiscalar, a Carnegie Mellon Stampede és a MIT M-gép.

Niagara - «ötvözet» MAJC és Hydra

A processzor UltraSPARC T1, ismertebb nevén Niagara, két fő prekurzor - Hydra és MAJC.

A '90 -es évek közepén, a nyomán a Java drag-specializált processzorok a Sun Microsystems által volt kísérlet arra, hogy hozzon létre egy processzor egy „nagyon hosszú szó» - vliw (VLIW). Ezt a kezdeményezést hívott MAJC (mikroprocesszor architektúra Java Computing). Mint más projektek, amelyek indult egy időben (Intel IA-64 Itanium), ebben az esetben az volt a feladat, hogy át néhány igen bonyolult műveleteket a fordító vezetése. Kiürített tranzisztor logika lehet használni, hogy több termelő funkcionális egységek (funkcionális egység), annak érdekében, hogy hatékony cseréjét parancsokat és adatokat a CPU, a memória és a cache memóriát. Így, hogy felszámolja a Neumann „szűk”.

MAJC eltér a legtöbb processzorok nem rendelkeznek speciális társprocesszorokat (alvállalkozók), amely általában az úgynevezett funkcionális eszközök teljesítő egész művelet, lebegőpontos és multimédiás adatok. Ez minden funkcionális egység ugyanaz, amely képes bármilyen művelet végzése egyrészt, csökkentette a hatékonyságát bizonyos műveletek, a másik megnövekedett felhasználási aránya a teljes processzor.

Niagara testesíti meg a legjobban a két alternatív megközelítések végrehajtását multi-threading - SMT és CMP. Első pillantásra nagyon hasonlít a Hydra, hanem lehet nevezni Hydra Niagara «elrendezés». Eltekintve attól a ténytől, hogy az utóbbi - kétszer annyi mag, amelyek mindegyike képes kezelni négy szál.

Saját megközelítés létrehozását többmagos processzor által kínált IBM Cell akinek projekt neve „chip heterogén többprocesszoros» (heterogén chip többprocesszoros). Cell architektúra is nevezik Cell Broadband Engine Architecture (CBEA). Cell többprocesszoros áll IBM 64 bites Power Architecture core és nyolc speciális társprocesszorokat hogy a program végrehajtása az „egy csapat a sok adat.” Ebben az építészet, az IBM az úgynevezett szinergikus processzor (SPU).

Lehet, hogy egy külön áramot processzor (Single-streaming processzor - SSP) és többszálú processzor (Multi-Streaming Processor - MSP).

Képviselői az vitathatatlan SIMD-processzorok tekinteni mátrix: Illiac IV, ICL DAP, Goodyear Aerospace MPP, Connection Machine 1 stb Az ilyen rendszerekben egy-szabályozó tanács, valamint a készülék figyeli a készlet feldolgozó elem-zsarukat. Minden feldolgozási elem kap a vezérlő készülék minden fix időben azonos oldali parancsot, és végrehajtja azt a helyi adatokat.

Egy másik reprezentatív osztály SIMD-vektor-WIDE processzorok, amelyek vektoron alapul obrabotkadannyh. Vektor feldolgozása megnöveli a processzor teljesítményét annak a ténynek köszönhető, hogy a feldolgozás a teljes adathalmaz (életkor tórusz) készül egy paranccsal. Vektor számítógépek ma nipuliruyut tömbök hasonló adatokat ugyanúgy, mint a ska-sarki gép feldolgozza az egyes elemek a Massey-szigeteken. Ebben az esetben meg kell vizsgálni minden egyes eleme a vektor külön adatfolyam elem. Amikor dolgozik vektor módban vektor processzor feldolgozza az adatokat szinte párhuzamosan, így többször is gyorsabb, mint amikor működik skalár módban. A maximális adatátvitel sebessége a vektoros formátumban lehet 64 Gb / s, ami 2 nagyságrenddel gyorsabb, mint a skalár gépek. Példák az ilyen típusú rendszer, például, a feldolgozók Hitachi és a NEC cégek

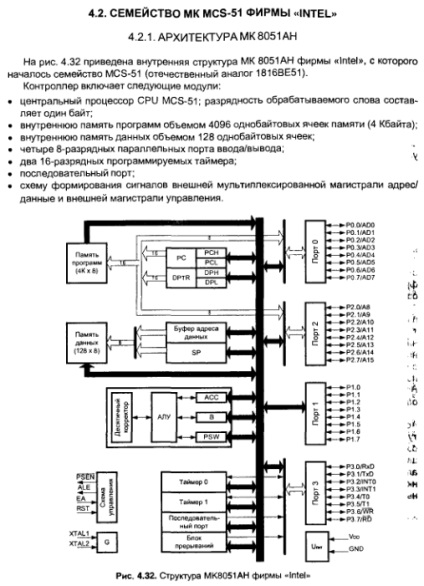

Kérdés # 6 "single-chip mikro-architektúra számítógép MCS-51 család"

A vezérlőegység (CU) irányító jeleket generál az autóbuszok valamennyi utasítást blokkok a gép.

Aritmetikai logikai egység (ALU) célja, hogy aritmetikai és logikai műveletek konverziós adatait. ALU általában két regiszter, egy összegző és vezérlő áramköröket. Vipera - végez kívül bemenetére táplált bináris kódokat. Regiszterek - gyors memória sejtek különböző hosszúságú. a vezérlő áramkör fogadja az utasításokat a busz vezérlő jeleket a CU és alakítják át jeleket működésének szabályozására a nyilvántartások és az összeadó. ALU végzi aritmetikai műveletek (+, -, *, :) alig több mint az egész bináris számokat.

Az interfész a mikroprocesszor.

válasszon a következő utasítás RAM-sejtek és parancsot fogadó nyilvántartásban;

dekódolja a műveleti kód;

olvasata a sejtek a ROM firmware vezérlőjelek eljárásokat meghatározó végrehajtó előre meghatározott működési és elküldése vezérlőjelek ezeket az egységeket;

eredmények rögzítése a memóriában.

A vezérlő áramkör busz és a portok funkciói a következők:

átveszi az adatokat a port: a menedzsment a kikötői állás, állapotát;

csatorna szervezet közötti adatátvitel a kikötő és a képviselő.

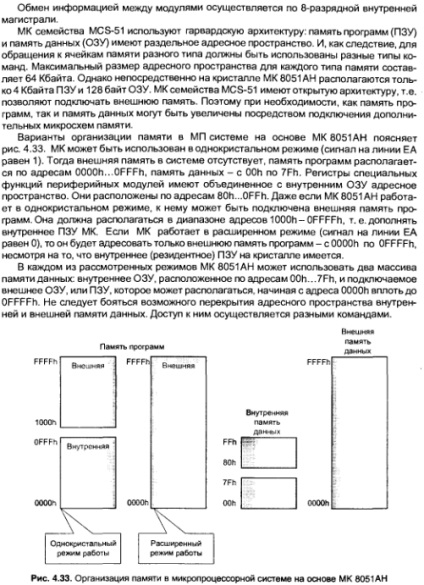

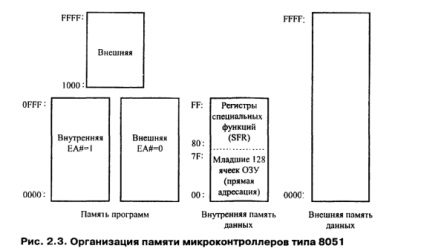

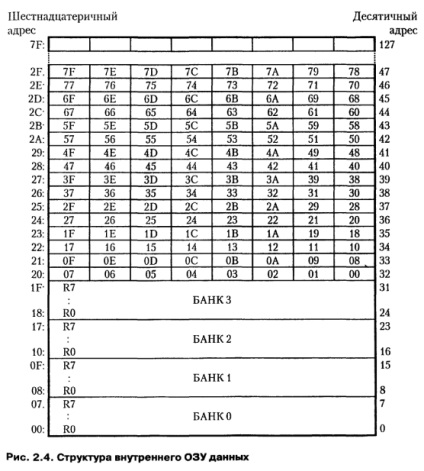

Kérdés # 7 „A szervezet belső és külső memória MS8-51”

Oh

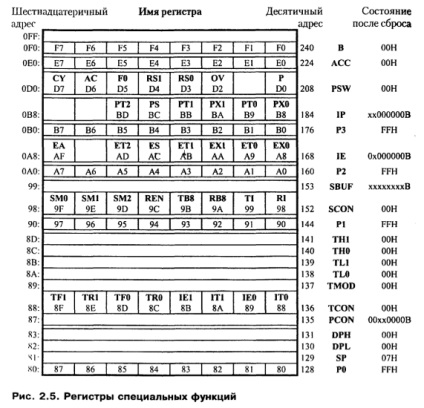

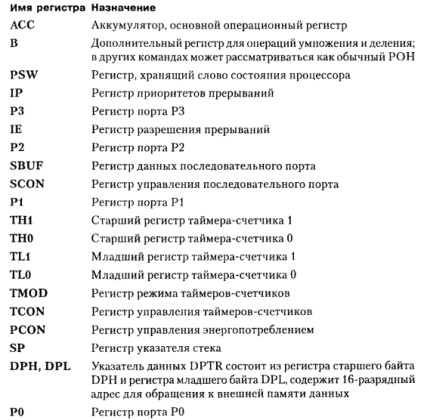

2.5 ábra mutatja a terület különleges funkció regiszterek. Ez magában foglalja az összes regiszter elérhető szoftver (kontroll és adat) vnutrennihblokov IO.

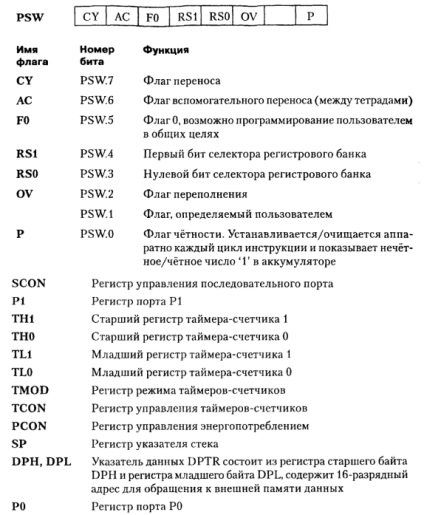

A formátum a speciális funkciók regiszterek felül kell vizsgálni a szakaszok szentelt a leírás a megszakítási rendszer és az egyes input-output funkció blokkok. Itt látható a formátum PSW regiszter tárolja a processzor állapotát szó. Ez a nyilvántartás az akkumulátor eredményét tartalmazza az utasítás.

A formátum a speciális funkciók regiszterek felül kell vizsgálni a szakaszok szentelt a leírás a megszakítási rendszer és az egyes input-output funkció blokkok. Itt látható a formátum PSW regiszter tárolja a processzor állapotát szó. Ez a nyilvántartás az akkumulátor eredményét tartalmazza az utasítás.

Kérdés # 8 „input-output portok MS8-51. Jellemzői a programozás. "