Dinamikus frekvencia eltolódás fázis pll

Dinamikus frekvencia eltolódás fázist PLL

Oldalunk már pár cikket a PLL.

PLL - ez egészen egyszerűen egy beépített FPGA óra. Ez lehetővé teszi az egyik bemeneti órajel szintetizálni több más egy előre meghatározott frekvenciával, terhelhetősége és, kívánt esetben, néhány kezdeti fáziseltolás.

Most akarok beszélni a lehetőségét, dinamikusan eltolja a fázisban az óra PLL. Ez a funkció a PLL az FPGA. a Cyclone III, Cyclone IV, a MAX10 és mások. Hogy megmondjam az igazat, én magam, és ez csak, hogy elolvastam ezt a funkciót a PLL. Épp mielőtt Ehhez nem volt szükség, és most van egy projekt, ahol szükség lehet. PLL fáziseltolódás - úgy néz ki, mint az egyetlen módja annak, hogy pontosan vezérlõjellel késések.

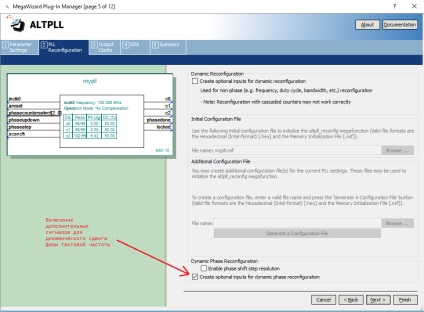

Tehát, egy varázsló van egy fül szám 2: PLL újrakonfiguráció. ott tesz egy csekket: Készítsen választható bemenetek dinamikus szakasz újrakonfigurálást.

Amint teszünk egy csekket a bal oldalon látható a varázsló PLL blokk és vannak új be- és kimenetek, amelyek korábban nem léteztek.

Ezek segítségével jeleket lehet szabályozni fázis bármely kimeneti órajel PLL.

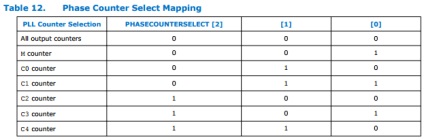

phasecounterselect jel [2..0] válassza ki, hogy mely belső számlálók PLL fog változni. A dokumentáció a PLL FPGA MAX10 van ilyen tábla:

Így, ha az szükséges, hogy eltolja a fázisban a kimeneti órajel c0, akkor annak szükségességét, hogy phasecounterselect = 3'b010. Ha a fáziseltolódás órajel c1, majd phasecounterselect = 3'b011.

A fáziseltolódás a kimeneti órajel által kezdeményezett beállításával phasestep logikai egységet. Ez a kezdete az ügylet fáziseltolódás. Egy „tranzakció” fázisban a kiválasztott frekvencia eltoljuk az egyik fázis egy lépésben (több erről később). A műszak végén órajelfázis PLL mutat phasedone jelet. Kívánt fáziseltolódás még, meg kell először az alacsonyabb phasestep logikai nulla, majd ismét egy lesz, mert a következő tranzakciót.

phaseupdown jel határozza meg az irányt a fáziseltolódás, előre vagy hátra.

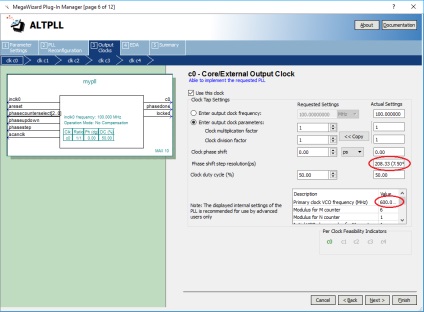

Most a fő kérdés: mennyit tudunk valójában elmozdulás a fázisban az óra? A dokumentáció egyértelműen kimondja, hogy a lépés fáziseltolódás - 1/8 időszak gyakorisága VCO PLL. VCO - belső feszültség-oszcillátort. Sajnos, a varázsló PLL nem lehet egyértelműen mutatják a kívánt Fvco frekvencia. Csak akkor látni, hogy mi történik a beállításokat.

Például, ha a bemeneti frekvencia 100MHz PLL kimeneti frekvenciája és PLL tettem 100MHz, a varázsló maga mondja, hogy Fvco belül a PLL 600MHz.

Ez azt jelenti, hogy a felbontás fázisban egy fázis óraeltolás lehet körülbelül 7,5 fok, ez lehet mozgatni az első frekvencia 208,33 picoseconds. Lehetséges, hogy növelje a felbontást?

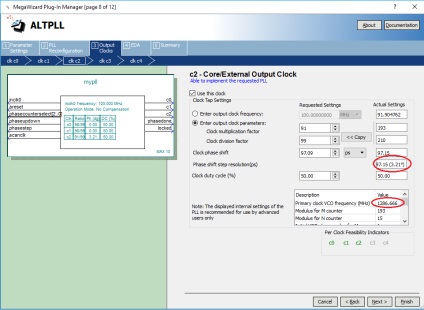

Sikerült felvenni ide azok a tényezők:

- hozam PLL c0, szorzó 98, az együttható Division 99, a kapott frekvencia

Ugyanakkor úgy látom, hogy Fvco = 1286,666MGts és felbontás fázis 97,15 ps. Ez egy nagyon nagy felbontású fázisban.

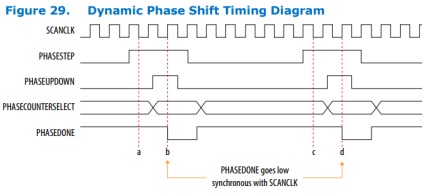

A dokumentáció a PLL van olyan idődiagram látható, amely, hogyan kell előállítani a dinamikus fáziseltolódás:

Azt javaslom, hogy próbálja meg ebben az esetben prosimulirovat ModelSim.

Én egy egyszerű projekt Intel Quartus Prime Lite, ahol szinte semmi, de a PLL és egy egyszerű logika, amely rendszeresen eltolja a fázisában a kimeneti frekvencia c1. felső szintű modul a projekt írtam Verilog:

modul felső (

bemeneti huzal KEY0,

bemeneti huzal KEY1,

bemeneti huzal CLK100MHZ,

INOUT drót [19: 0] IO,

kimeneti vezetéket [7: 0] LED

);

huzal wc0;

huzal wc1;

huzal wc2;

huzal wlocked;

huzal wpdone;

reg phase_step = 1'b0;

mypll mypll_ (

.areset (1'b0),

.inclk0 (CLK100MHZ),

.phasecounterselect (3'b011),

.phasestep (phase_step),

.phaseupdown (1'b1),

.scanclk (wc0),

.c0 (wc0),

.c1 (wc1),

.c2 (wc2),

.zárva (wlocked)

.phasedone (wpdone)

);

reg [3: 0] cnt = 0;

Mindig @ (posedge wc0)

cnt <= cnt + 1;

Mindig @ (negedge wc0)

if (CNT == 4'hF)

phase_step <= 1'b1;

más

if (wpdone == 1'b0)

phase_step <= 1'b0;

rendelni LED = 0;

rendelni IO [0] = wc0;

rendelni IO [1] = wc1;

rendelni IO [19: 2] = 0;

Csinálok egy ilyen projekt Marsohod3bis kártya és chip FPGA MAX10. Szóval van itt olyan bemeneti jelek KEY0 és KEY1, amelyet nem használnak, de hadd legyen. LED kimeneti jel nem használt, de a kimenetek IO [0] és IO [1] hoztam a kimenetek C0 és C1 a PLL. Ez az volt, hogy kényelmes megfigyelni a szimulátorban.

Itt, a projekt minden folyamatok játszódnak gyakorisággal c0, és ugyanazzal a kulccsal alkalmazzák scanclk. A bomlása azonos frekvencián meg és állítsa vissza phase_step.

Testbench szimuláció nem csinál semmi különöset, nos, ez csak akkor szolgáltat a vizsgált modul az eredeti órajel 100MHz.

`Időskála 1ns / 10PS

// vállalnak az alap órajel 100MHz

reg clk;

kezdeti clk = 0;

mindig

# 5 clk =

drót [7: 0] w_led;

drót [19: 0] w_io;

top top_inst (

.CLK100MHZ (CLK),

.KEY0 (1'b1),

.KEY1 (1'b1),

.IO (w_io),

.LED (w_led)

);

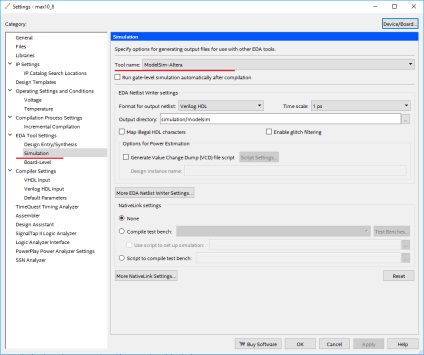

Mert én szeretnék látni egy szép kis óra fázis eltolással, akkor azt természetesen akarta tartani egy ideiglenes projekt szimulációs ModelSim. Ehhez már a projekt beállításainak hogy fogom használni a ModelSim-Altera szimuláció. Ugyanakkor azt várják, hogy a generált kimeneti fájlokat SDO vagy SDF-projektekre.

Sajnos az én kvartus más véleményt.

Ha összeállítja a projekt, akkor a következő üzenetet jeleníti: Figyelmeztetés (10905): A generált az EDA funkcionális szimulációs hálójegyzékkel, mert ez az egyetlen támogatott hálójegyzékkel típusú ehhez az eszközhöz. Kiderült, hogy az MAX10 chipet, csak akkor lehet csinálni funkcionális szimuláció? Kvartus generált csak én top.vo fájl

Amit látok, az idődiagramoknál: Modul rendszeresen felül ki phase_step jel és a PLL rövid impulzus megegyezik nulla phasedone jelet.

Ha zoom és próbálja vizsgálni több fázisú órajel frekvenciát, azonnal nyilvánvalóvá válik, hogy a jel fázisa IO [1], amely már a kimenetre kötött PLL c1 halad előre után azonnal phasedone jel:

Kiderült, hogy a szimuláció azt láthatjuk, hogy a fázis a clock eltolódik. By the way, vegye figyelembe, hogy milyen kicsi fázis lépésben képest az időszak a frekvencia is. fáziseltolódás hatása is próbálja használni mérése áramkörök késedelem sinalov a reflektométerek és egyéb mérőeszközök.

Megpróbálom, hogy a projekt egy egyszerű mérőműszert, amely képes értékelni a jel terjedési késleltetés pontossággal körülbelül 100 ps.

Ha megavizarde tick „lehetővé fáziseltolódás lépés felbontású”, akkor könnyebb irányítani a VCO frekvenciáját. Kimenő frekvencia megadható forduló - 100 MHz-es és fáziseltolódás lépés felbontás „- 96ps a 1300MGts VCO, 104ps számára 1200MGts VCO és így nem kell toeing foszlányok ..

Felveheti testbench a projekthez, és állítsa NativeLink beállítás „Fordítsd bevizsgálóasztal”. Ezután a szimuláció működni fog egy kattintással (Eszközök -> szimulációs eszköz -> Futtatás RTL Siumulation), akkor nem kell létrehoznia projektek és add könyvtárak ModelSim, hogy működni fog „out of the box”.

„Megpróbálom, hogy a projekt egy egyszerű mérőműszert, amely képes értékelni a jel terjedési késleltetés pontossággal körülbelül 100 ps” - várja, hogy!

10Gvyb / s, de a keze nem érte el.